| School of Science                   |                                                      |

|-------------------------------------|------------------------------------------------------|

| Master's Programme                  | in Information Networks                              |

|                                     |                                                      |

|                                     |                                                      |

| ohannes Vainio                      |                                                      |

| onannes vaimo                       |                                                      |

| Physically Un                       | clonable Functions as Trust Anchors for              |

|                                     | nbedded Device Security                              |

|                                     | inocuated Bevice Scenific                            |

|                                     |                                                      |

|                                     |                                                      |

|                                     |                                                      |

|                                     |                                                      |

|                                     |                                                      |

|                                     |                                                      |

| Master's Thesis                     |                                                      |

| Master's Thesis Espoo, May 22, 2018 |                                                      |

|                                     |                                                      |

|                                     |                                                      |

|                                     | N. Asokan, Professor                                 |

| Espoo, May 22, 2018  Supervisor:    | N. Asokan, Professor Antti Kettunen, Ph.D. (Physics) |

| Espoo, May 22, 2018                 |                                                      |

| Author: Johannes Vainio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title of the thesis: Physically Unclonable Functions as Trust Anchors for Connected<br>Embedded Device Security                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| umber of pages: 48+15 Date: May 22, 2018                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| Major: Information Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| Supervisor: N. Asokan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                 |

| Thesis advisor: Antti Kettunen, Ph.E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D. (Physics)                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                 |

| Physically Unclonable Functions (Plyproblems in current embedded devicunmonitored areas accessed over the communications require secrets on easily be read during transit from a fixed A PUF can be thought of as a mech from something that cannot be copicand evaluate an FPGA PUF that can unclonable, reliable entropy from me frequencies deployed on the FPGA submicroscopic silicon chip manufactolerances and cannot thus be copically to the PUF can be used as a device the cryptosystems, in turn making it post channels without any "leaps of faith" | ce security. Devices ane untrusted public in the device, but simple factory to the deployn anism for extracting ced or cloned. In this the produce an estimate easuring slight variation fabric. The frequency cturing variations that ed. | are often deployed in ternet. Confidential e persistent memory can nent by untrusted personnel deterministic randomness nesis, we design, implemented 250 bits of physically ons in ring oscillator variations result from the below manufacturing a stable basis for various devices and initiate encryptores. |

| Keywords: Physically Unclonable For PUF, trust anchor, embedded device security, FPGA, SoC, device attests authentication, challenge-response                                                                                                                                                                                                                                                                                                                                                                                                                     | e security, IoT<br>ation, device                                                                                                                                                                                                           | Publishing language:<br>English                                                                                                                                                                                                                                                                                 |

| Acknowledgements             | 3  |

|------------------------------|----|

| Acronyms                     | 4  |

| Glossary                     | 4  |

| 1 Introduction               | 5  |

| 2 Background                 | 6  |

| What is a PUF?               | 6  |

| Benefits of using a PUF      | 8  |

| Common PUF designs           | 10 |

| 3 Problem definition         | 14 |

| Use case                     | 14 |

| Threat model                 | 14 |

| Requirements                 | 15 |

| Selected concept             | 16 |

| 4 Methodology                | 18 |

| Technical methods & design   | 18 |

| Device                       | 18 |

| Our PUF design               | 18 |

| Modules                      | 21 |

| Oscillator selection         | 21 |

| Data collection              | 25 |

| Running order                | 27 |

| Tools and languages          | 27 |

| Analysis methods             | 28 |

| Measurements                 | 28 |

| Sources of error             | 29 |

| 5 Evaluation                 | 32 |

| Measurements                 | 32 |

| LISA                         | 35 |

| Sources of undesirable error | 36 |

| Fulfillment of requirements  | 44 |

| 6 Discussion                 | 46 |

| 7 Related Work               | 50 |

| RO-PUF designs               | 50 |

| References                   | 53 |

| Appendix                     | 56 |

# Acknowledgements

Greatest thanks for this thesis go to my thesis supervisor Antti Kettunen for his time and mental energy in keeping up the constructive criticism as I kept writing about distance measures, positional errors and other tedious PUF details. I would like to thank Juhani Mäkelä for preparing and suggesting this subject. As my lack of background in this kind of "real" engineering made me suspect my chances with this topic, I am grateful for the trust that was placed in me. Thanks belong also to Nixu Corporation for allowing me to use company time and equipment for this thesis.

# Acronyms

ASIC Application-Specific Integrated Circuit

CLB Configurable Logic BlockCPU Central Processing UnitCRP Challenge-Response Pair

FPGA Field-Programmable Gate Array

**LISA** Longest Increasing Subsequence Algorithm

LUT Look-Up TableMUX (De)MultiplexerPL Programmable Logic

**PRNG** Pseudo-Random Number Generator

**PS** Processing System

**PUF** Physically Unclonable Function

RO Ring OscillatorSoC System on a Chip

RRAM Resistive Random Access MemorySRAM Static Random Access MemoryTRNG True Random Number Generator

# Glossary

Basic Element FPGA primitive; most commonly a LUT, a Register or a MUX.

**Bitstream** FPGA configuration data

Challenge The input of a PUF evaluation; see CRP

**CLB** Modular FPGA component. Contains two Slices and one routing matrix.

**CRP** A PUF input and its associated expected output.

**FPGA** An integrated circuit containing configurable logic components.

**Inverter** A NOT logic gate; inverts its input

LISA A sequencing algorithm presented by Yin & Qu (2010).

LUT A Basic Element that can be configured to act as any logic

gate.

**MUX** A multiplexer has a signal input, selector input and many alternative

outputs. The value of the selector input decides to which output the signal input is routed to. Demultiplexers have many inputs and one output.

PL Name for an FPGA on an embedded device

PS Name for a CPU on an embedded device

**Register** on-chip memory; single-bit registers are also Basic Elements.

**Response** The output of a a PUF evaluation; see CRP

**RO** A combination of logic gates that outputs an oscillating signal

Routing matrix FPGA component controlling the connections between Basic Element pins.

Slice A modular FPGA component. Contains a small number of Basic Elements.

SoC A name for a chip that integrates several components, allowing it to act as a

complete system.

# 1 Introduction

The purpose of this Master's thesis is to determine the feasibility of implementing a practically viable Physically Unclonable Function (PUF) in a field-programmable gate array (FPGA), by attempting to do so. Our use case is to use the PUF as a trust anchor, the source of trust for cryptographic operations performed on the device. The requirements for PUF performance will be defined in more detail in relation to our use case.

PUFs are based on exploiting physical random variations that are often intrinsic to the device. A silicon PUF is a circuit designed for amplifying these unpredictable submicroscopic manufacturing variations on a silicon chip. Our PUF design uses frequency differences of ring oscillators (ROs), caused by this variation in FPGA silicon chips, to calculate physically unclonable output bits.

Our target device is the Avnet MiniZed board (Avnet n.d.), which carries a Zynq7000 system-on-a-chip (SoC). The Zynq has, among other things, both a programmable logic (PL) block containing the FPGA and a processing system (PS) containing a normal microprocessor (CPU), making it possible to build complicated systems without leaving the chip. Our PUF was deployed on five MiniZed boards in order to evaluate our PUF's behavior on different chips. Analysis has been performed to evaluate the quality of our PUF using measures presented in academic literature.

Given an input challenge, a PUF calculates a deterministic but hard-to-guess response. In other words, the PUF's behavior should be reliable but unpredictable. It should not be possible to predict the behavior of the same function on any other device, and it should not even be possible to manufacture such a device, due to the variations existing on a scale below manufacturing tolerances. The PUF will use challenge-response pairs (CRPs) generating responses with at least enough combined entropy to be suitable for use as unique device fingerprint or trust anchor.

# 2 Background

# What is a PUF?

A PUF is a *function* that turns an input (called a *challenge*) into an output (called a *response*), usually with some uncertainty. A PUF extracts randomness from something physical: in our case, this source will be sub-microscopic manufacturing variations in an FPGA silicon chip. The extracted randomness can be measured using the concept of entropy (Maes & Verbauwhede 2010). A PUF can also be thought of as a "device fingerprint", as it can be used to uniquely identify a device. The concept of PUF was first introduced by Pappu et al. (2002) under the name *physical one-way function*.

A *trust anchor* is an entity in a cryptographic system that is assumed to be trusted, rather than have its trust derived from some other entity (IETF 2016). In the context of public-key cryptography, a trust anchor is defined as "[...] an authoritative entity represented by a public key and associated data" (IETF 2010). In the context of trusted platform modules, where a co-processor continuously records the software state of a system, the first measurement during a boot uses a trust anchor, that often is the system firmware (Abera et al. 2016). Trusted platform modules in turn often act as trust anchors for larger systems (Schmidt et al. 2008). PUFs are well suited for use as trust anchors due to being unclonable, unpredictable and hardware-based.

The physical variations that PUFs are based on are often made visible by slight but deterministic differences in objects that have been designed to be identical. For example, on integrated circuits the small variations caused by manufacturing processes cause behavioral effects such as different signal speeds or varying memory cell settling behavior across design-identical components. Different PUF designs extract the variations from physical objects in different ways. Our PUF will be based on differences between the speeds of design-identical ring oscillators placed on an FPGA.

The concept of a challenge-response pair (CRP) is central in the theory of PUFs. A PUF can support a varying number of challenge-response pairs. The challenge and response can be single bits, or arbitrarily long. A PUF should always produce as close to the same output as possible on the same device, and an unpredictably different output on any other device.

The CRP behavior of a PUF can be formulated as (Maes & Verbauwhede 2010):

PUF(Challenge) -> Response + random variation

Due to the possibility of bit flips, a random variable should be added to the equation to depict the fact that bits in the response may get flipped from the expected value. The challenge can affect the response generation in various ways, depending on the design of the PUF. In our case, the challenge will consist of two values used to select ring oscillators.

A PUF that is based on the physical properties of something is called an intrinsic PUF, and PUFs based on chip variations are called silicon PUFs. While there are PUFs that are not based on silicon chip variations, including optical PUFs, coating PUFs and even "paper PUFs", we will limit our scope to intrinsic silicon PUFs (Maes & Verbauwhede 2010).

#### **Enrolling procedure**

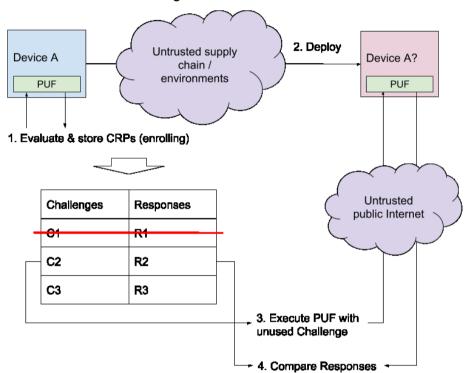

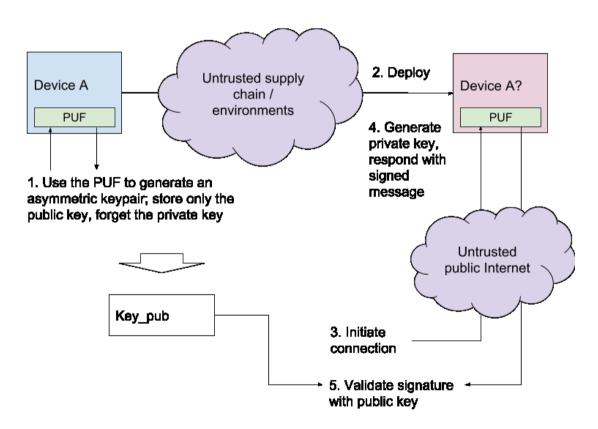

In order to know what the correct response to a challenge is, the PUF should be enrolled. In the enrolling procedure, all the CRPs that are planned to be used when the device is deployed should be evaluated and stored. Depending on the method used, unreliable bits might be filtered out in this phase by simply excluding them from being used as challenges. After enrolling all CRPs we want to use, a PUF can be used for for simple authentication of deployed devices as is shown in figure 1.

**Figure 1**: An example of a simple PUF-based device authentication scheme with single-use CRPs (Suh & Devadas 2007).

## **Properties of a PUF**

According to Maes and Verbauwhede (2010), an ideal PUF has seven properties presented in table 1. On the other hand, Zhang et al. (2014) recognize only three more coarse-grained properties: *Persistent and Unpredictable*, *Unclonable* and *Tamper Evident*. The first covers Maes and Verbauwhede's properties 3 and 5. *Unclonable* and *Tamper Evident* are exact matches. Zhang et al. do not include *One-way* in their properties, while property 1 is assumed given. Their view on property number 2 is unclear.

Of these seven properties, tamper evidence is particularly hard to achieve on general-purpose FPGAs, as current physical attacks (Lohrke et al. 2016, Zhang et al. 2014) can read and measure FPGA elements without physical contact. Here unclonability means unclonability in the physical sense, but attackers can bypass physical cloning by either characterization or modeling attacks, which we discuss later.

|   | Property  | Explanation                                              |  |

|---|-----------|----------------------------------------------------------|--|

| 1 | Evaluable | A PUF should be able to produce responses to challenges. |  |

| 2 | Unique         | It should be always possible to identify a PUF instance by its CRP behavior.                                                                                             |  |

|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3 | Reproducible   | The same challenge on the same PUF should always produce the same, or very similar, response.                                                                            |  |

| 4 | Unclonable     | It should be very hard to move or copy the function from its physical environment. On silicon PUFs, this is achieved by using small, uncontrollable chip irregularities. |  |

| 5 | Unpredictable  | It should not be possible to predict the response to a CRP from observing other CRPs on the same PUF or some other instance of the PUF.                                  |  |

| 6 | One-way        | It is not possible to reproduce the original challenge from an observed response.                                                                                        |  |

| 7 | Tamper evident | (Physical) attack attempts should leave traces, possibly altering the behavior of the PUF.                                                                               |  |

Table 1: Properties of an ideal PUF

# Benefits of using a PUF

The motivation to use a PUF is usually device authentication or key material generation, to be used for either protecting data or intellectual property. Since the source of entropy is the physical chip, a PUF can be used both as-is to uniquely identify a chip, and also as a part of a cryptographic system to provide device-specific secrets. Key material from a PUF can be used in a wide variety of cryptographic applications, including symmetric and public-key cryptography. Combining these mechanisms can allow for ensuring both the confidentiality and integrity of the device contents and communications, and integrity of its identity.

Physical security is a challenge for embedded devices. While the complex data centers where much of today's cloud computing happens are usually under strict physical security, an embedded device might be deployed in any vehicle, building or public space, where access to it might not be controlled, or controlled by a third party.

For the use case of establishing a secret on a deployed embedded device, using a PUF has a number of benefits as compared to either using a stored secret, a true random number generator or a pseudo-random number generator.

#### Benefits over a stored secret

A secret or key held in non-volatile memory can potentially be read either programmatically or physically. In case a remote software-based attack can be developed, for example by exploiting a software vulnerability, it is often easily scalable to all devices of the same type. Supplier security should also be taken into account, as malicious contractors or suppliers can read hard-coded device serial numbers or keys stored in flash memory during transit and deployment. Specialized physically protected chips might be explored as a solution.

#### Benefits over a TRNG

It is possible to implement a True Random Number Generator (TRNG) in an embedded device, using for example analog noise measurements from a temperature sensor. This true randomness could be used to generate unpredictable keys. However, unless we compute and store the key on the device before deployment, we have no way of knowing what key the deployed device will have. Furthermore, there is no way of generating the same key twice, so the generated key would have to be stored.

When we don't know what key the device has, our only option is to trust the connection claiming to be the device on the first use (Trust On First Use; TOFU). After a TOFU connection has been established, it is secure, but if an attacker intercepts or spoofs the first request, all future traffic can be compromised. Using a PUF allows us to know beforehand what the key, trust anchor or identifier will be, thus allowing us to establish a trusted channel from the start.

#### Benefits over a PRNG

A Pseudo-Random Number Generator (PRNG) produces random-looking but predictable numbers given a seed value (Maes et al. 2012). A PRNG takes a seed value as input and outputs statistically random but deterministic output. Using PUFs on a set of devices can be thought to bear some resemblance to using PRNGs with a unique seed value on each device. However, the usefulness of PRNG-backed cryptography is severely restricted by the need of keeping the seed secret, thus providing little benefit over a stored key (Maes et al. 2012). A PUF does not require us to rely on such a brittle secret, as the randomness is embedded in the chip itself.

As such, using a PUF for cryptography has benefits in that (Maes et al. 2012):

- 1. We do not need to store sensitive keys in memory, as the PUF can regenerate the secret at any time.

- 2. The PUF is bound to a single physical chip, so it cannot be stolen except by full characterization or modeling of the PUF.

#### Attacking a PUF

A good PUF should remarkably improve the situation compared to any of the methods discussed above. While a PUF is very hard or impossible to clone, attacking a PUF is possible by other means. Attacks against PUFs include modeling attacks and characterization attacks (Rührmair et al. 2013; Maes & Verbauwhede 2010).

Modeling attacks are based on building a software model of the behavior of the PUF, with the help of tools like machine learning. Performing this kind of attack requires visibility into unobfuscated CRPs, but will compromise also other CRPs before they have been used.

Characterization attacks are based on collecting CRP behavior or physical measurements that can be directly used in attacking later CRPs. Characterization does not lead to the ability to predict unseen CRPs, but being able to run and store all CRPs might lead to the ability to masquerade as the PUF, even if the CRPs are obfuscated.

Zhang et al. (2014) separate non-modeling attacks further into *side channel* attacks and *physical cloning* attacks. They consider the SRAM attack by Helfmeier et al. (2013) the only

successful physical cloning up to that date, while other methods based on measuring, timing or power manipulation they consider side-channel attacks.

# Common PUF designs

#### **Arbiter PUF**

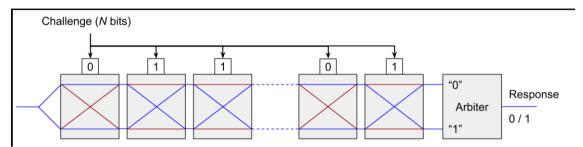

**Figure 2**: An Arbiter PUF. Blue lines represent signal routing. Challenge bits determine the routing within each element.

The first delay-based silicon PUF design is the Arbiter PUF proposed by Lim et al (2005). It is based on configurable delay lines, producing 1 if the line "1" was faster and 0 otherwise. Figure 2 demonstrates the signal routing behavior on a block level. Cross-coupled NAND gates are often used in the arbiter block to determine the faster signal.

The main weakness of the Arbiter PUF is its susceptibility to model-building attacks using machine learning. Due to the simple design's vulnerability more complex combinations of delay lines and logic gates have been proposed. These more complex combinations are more resilient but even these have been shown to be learnable (Rührmair et al. 2013).

The large sensitivity of the Arbiter PUF to routing differences makes it unsuitable for our target FPGA device. Arbiters require additional configurable delay lines to calibrate them correctly on an FPGA; on an ASIC, accurate controlling of the route design length is possible, so that any variance is caused by random process variation.

## **Butterfly PUF**

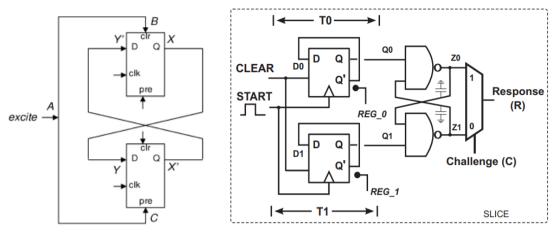

The Butterfly PUF first proposed by Kumar et al. (2008) is based on two cross-coupled latches or flip-flops. Figure 2 presents a gate-level representation of the design. The excitement signal sets the other latch to logic-1 and resets the other to logic-0. Due to manufacturing variations, the state of both latches will settle on either value.

Figure 2 (left): the Butterfly PUF (Morozov et al. 2010)

Figure 3 (right): the Ultra-Compact Identification Generator (Chongyan & O'Neill 2015)

## The Ultra-Compact Identification Generator

A design by Chongyan & O'Neill (2015) called the "ultra-compact identification generator" (figure 3) is also based on two flip-flops, the output of which is passed to two cross-coupled NAND gates. The NAND gate to first receive the signal from the flip-flop will determine the output of the bit unit. The proposing article places emphasis on the feasibility of FPGA deployment and compact footprint. Generating a single bit unit on an FPGA requires two registers and two *Look-Up Tables* (LUTs) configured as NAND gates. Selection logic can be added after the registers to make different pairings, allowing different challenges to be used.

#### **SRAM PUF**

Static Random-Access Memory (SRAM) PUFs are based on the settling behavior of SRAM memory bits (Kumar et al. 2008; Aysu et al. 2015; Herder et al. 2014). An SRAM cell (figure 5) is based on cross-coupled inverters that use positive feedback to maintain their state. Without a write operation, bits in SRAM tend to settle as either 0 or 1, and this tendency is determined by random process variations. SRAM PUFs are not viable on many modern devices, including the MiniZed board, due to the device resetting all memory to zero at power-up. SRAM PUFs have been demonstrated to be vulnerable to cloning (Helfmeier et al. 2013).

Figure 4 (left): Anderson's glitch PUF (Anderson 2010)

Figure 5 (right): an SRAM cell

#### **Glitch PUF**

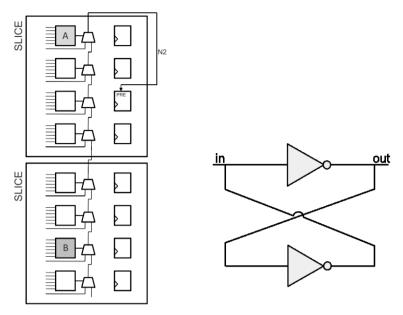

Glitch PUFs are based on a signal spike (called a glitch), usually generated by signal speed variation caused by random process variation on a design-identical route. Anderson's (2010) FPGA-friendly PUF is an example of this concept. Many PUFs are very sensitive to routing asymmetries, and it is hard to guarantee symmetrical routing on FPGAs. To that end, this PUF is based on the binary arithmetic carry chains present in Xilinx FPGAs (see figure 4). Each of his PUF's bit units operate within two adjacent *Slices*, where there is a dedicated wire between the carry chains; the connection between them does not go through the routing matrix. The glitch is generated by the difference in the speeds of LUTs A and B when transitioning to the other logic state. Distance between the LUTs determines the length of the glitch pulse. Anderson saw the lack of cross-device portability of designs as a problem, and thus he openly provides the source code of his design, to help in the evaluation of PUF designs in literature.

# Ring oscillator PUF Counter Comparer Response

Figure 6: A ring oscillator PUF (Suh & Devadas 2007).

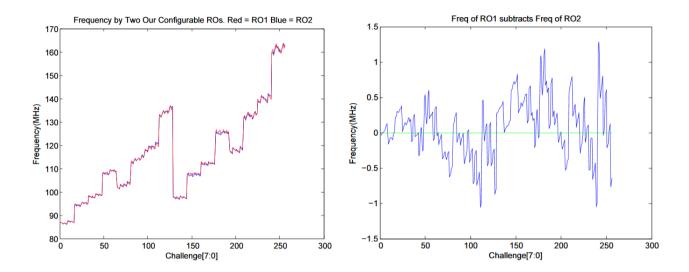

The ring oscillator PUF (RO-PUF) is based on the fact that random manufacturing variations have an unpredictable and measurable effect on the frequencies of ring oscillators, usually enough to overcome random noise and environmental effects. As the effect is random but deterministic, PUFs can be built using this behavior. The earliest version of a RO-PUF was proposed by Gassend et al (2002); in their concept, the challenge alters the signal routing (similarly to the Arbiter PUF) within each of a pair of ring oscillators, and oscillator pair frequencies were then compared to determine the faster oscillator and thus the output bit. As their design shares the additive delay characteristics with the Arbiter PUF, it is vulnerable to the same modeling attacks (Maes & Verbauwhede 2010).

Challenge

The design that has since become the baseline RO-PUF design in the literature was proposed by Suh & Devadas (2007), shown in figure 6. Their design differs from Gassend et al. in that all oscillator routings are designed identical, and the challenge selects which RO units are to be compared. The RO frequencies are again compared with each other, and the output bit is again decided based on which oscillator was measured to be faster. *N* ring oscillators are deployed on the FPGA, each connected to a pair of demultiplexers. The challenge is used as the selector input for the demultiplexers, thus selecting which oscillators are connected with the edge counters. When the PUF is powered, the edge counters count the number of rising signal edges that are output by the two ring oscillators selected by the challenge. After either a specified oscillation count is reached or certain period of time has elapsed, the PUF is powered off and the counts are compared to determine the output bit. RO-PUFs have achieved good measurement results in the literature (Maiti & Schaumont 2010; Maes et al. 2012).

# 3 Problem definition

# Use case

Our use case is to calculate an adequate number of unpredictable, unique, physically unclonable bits to build a device-specific secret that is suitable to use as a device trust anchor. This secret trust anchor allows us to setup confidential communications with the device while being certain of its identity. A PUF enrolling procedure will be performed in a trusted environment before deployment.

In the conceptual use case scenario for the purposes of this thesis, the device is to be deployed in the field in an environment that is relatively safe (e.g. a normal locked room) but not controlled by us (e.g. on someone else's premises). We are connected to the device over the public internet, which is untrusted. We will not have physical access to it most of the time, but we can arrange visits with advance notice to maintain or replace the device.

It is a fact of cybersecurity is that there can never be perfect protection against an attacker who has physical access, time and money. With a PUF, we can aim to make these kinds of attacks as hard to perform and scale as possible. It should be possible to make the attack require similar physical access to each new attacked device, possibly requiring removal from deployed site and leaving tamper evidence in the process.

## Threat model

There are three assets we are trying to protect:

- Cryptographic identity of the device

- Confidentiality of device data and communications

- Cryptographic identities of other similar deployed devices

Furthermore, the threats our device is facing can be divided into three categories:

Network threats. Relevant network attacks include for example spoofing and man-in-the-middle (MITM) attacks. In a spoofing attack, someone might pretend to be our device in order to receive legitimate communications. In a MITM attack an attacker intercepts and possibly manipulates communication packages to and from the device.

*Malicious software.* An attacker might get software to run on the device using e.g. a vulnerability in 3rd party software on the device, or through physical access. Malicious software insertion should be mitigated using standard best practices in hardening and software updating. This attack can be quite cost-effective compared to a true physical attack.

*Physical attacks.* An attacker might steal a device, take it into a laboratory test bench, and start probing it with physical sensors. Physical attacks can e.g. read and manipulate secrets on the chip and board memory.

# Requirements

#### R1: Adequate entropy with no fundamental weaknesses

The length of the bit string should be long and unpredictable enough to provide adequate entropy for robust cryptography. While 128 bits of entropy should be safe for the foreseeable future, 256 bits of entropy is guaranteed to be enough against any brute-force attack due to fundamental limitations arising from physics (Schneier 1999, 2013).

The design should not have any inherent remotely exploitable vulnerabilities or other fundamental weaknesses, such as being susceptible to modeling attacks, and should be as resistant to physical attack as is reasonably possible. The design concept's potential for further hardening should be included in this consideration.

**R2:** Maximum reliability and longevity within the expected operating environment PUF reliability means the response from a PUF instance is always the same. We are aiming for 100% reliability, which means that the PUF evaluated on the same device should always return the same identical response, and never flip any of its bits under the expected operating conditions.

In our case, reliability of the response is prioritized over the number of usable bits, challenge-response pairs and even entropy. If each PUF instance returns exactly the correct response, we can avoid implementing error-correction methods. The PUF should remain usable for as long as possible, preferably 10 years, and give advance warning of aging deterioration.

The PUF should remain reliable under temperatures varying within the predicted operating temperature range. The effect of altered voltages on reliability will not be considered in our evaluation, as voltage is non-trivial to alter on our test device, and this effect not central to our use case.

#### R3: Reasonable efficiency

It is possible that some bits in the PUF output are predictable, and thus contribute less than a full bit of entropy to the response. A perfectly efficient PUF would have only response bits that produce close to one bit's worth of entropy each. We can estimate efficiency using *entropy density*, calculated as the ratio of produced bits and the entropy carried by them (Maes et al. 2012). It is possible to achieve an adequate amount of entropy (**R1**) using either a smaller number of high-quality bits or a larger number of lower-quality bits. We shall later estimate the entropy for an attacker with full knowledge of bit-specific biases.

## R4: Scalability and portability of design

All parts of the system should be designed so that it is as widely applicable to different devices as possible, including near-future ones. The design should be easy to increase in size. The PUF should be as agnostic of underlying hardware specifics as possible, and it should be cheap and easy to deploy on new devices.

## R5: Understanding the sources of error

We will research the sources and effects of error in the behavior of our PUF. While this is not strictly a requirement on the PUF implementation, since the implementation is unlikely to be

perfect, it is important to measure and understand the different sources of error that prevent our PUF from performing ideally. This builds trust in the implementation and lays the groundwork for future improvements on the PUF design.

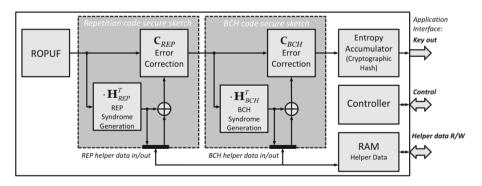

# Selected concept

The concept we have selected for our implementation is a controlled ring oscillator PUF with software-readable oscillation counter registers. Using software running on a CPU in conjunction with a PUF is known as a Controlled PUF or CPUF (Maes & Verbauwhede 2010). This "RO-CPUF" concept was selected for its following good qualities that help us achieve our requirements:

- Relative resilience against attacks (R1). Arbiter PUFs have been shown to be very vulnerable to model-building attacks due to the fact that every observed CRP evaluation reveals information that is also used in the generation of other CRPs (Rührmair et al. 2013, Maes 2013: 110). SRAM PUFs have been attacked using a Focused Ion Beam (FIB) and measuring leaking Near Infrared photonic emissions, leading to a complete characterization (Helfmeier et al. 2013). Meanwhile, Herder et al. (2014) report only two RO-PUF attacks, one manipulating the frequency of the oscillator by driving a signal on the ground plate, and another physically measuring the oscillations. The first is a non-issue for us because the attack would have to happen in the enrolling phase; the second is defeated by multiple oscillators running simultaneously in close proximity, which will happen in our design. More recently, however, RO-PUFs have been successfully attacked using Laser Voltage Probing (Lohrke et al. 2016), making it relevant to consider mitigations against direct frequency measurements.

- Good measurement results in literature (R1, R3). In literature, RO-PUFs have reported the best reliability and unpredictability measurement results when compared to implementations of the other basic designs (Maes 2013: 115, 125). Reliability measures have been good, which is a priority to us.

- Modularity and scalability (R4). On an FPGA we do not have precise control over the physical routing of signals in the chip, as we might have when designing an ASIC. For example, Arbiter PUFs are very sensitive to routing error, making them unsuitable for FPGAs. As each oscillator unit is modular and has an identical internal component layout, we can assume that the internal connections are also identical in design. Implementing a ring oscillator requires only an odd number of NOT gates, one AND gate and in our case one OR gate. These can easily be implemented using the configurable look-up tables (LUTs) that normally make up the bulk of elements on any FPGA. This is in contrast to e.g. the exotic memristor PUF (Mazady et al. 2015). The RO units are also reasonably compact, each occupying 7 of the 8 LUTs present in a single CLB. Increasing the number of oscillators is simply a matter of adding them and making the selection logic accommodate larger selectors.

- On-chip controllability (R3, R2). Our design can be controlled from the on-chip processor. We can choose from the software which RO units to run, in which order, and for how long. When we have an established a trusted channel, we can even remotely configure

the processor to use new challenges for the PUF, or run diagnostic runs to detect PUF aging. We can also potentially perform pre-processing and post-processing on the PS while remaining on the same chip, increasing the security performance.

- Scalar output (R2, R5). While for example a Glitch PUF or Butterfly PUF is based on simple units producing just 0 or 1, we have the benefit of collecting absolute measurements from our oscillators. Acquiring raw speed data about the oscillators instead of only the final output bits allows us to make our enrolling method robust and predictable with greater confidence and fewer measurements. Scalar data combined with controllability also adds the option of adjusting the run length, while containing more information about the underlying chip variation. However, while easing development and enrollment, on a deployed device this feature increases the attack surface, leading to considerations if the enrollment and deployment should use different FPGA configurations.

# 4 Methodology

# Technical methods & design

# Device

Our target device is the Avnet MiniZed containing a Xilinx Zynq-7000 SoC chip. The chip contains both a programmable logic (PL) and a processing system (PS) section. The PS contains a single ARM Cortex CPU. The board was chosen due to it containing a widespread, established and modern chip and its affordable pricing, making it possible to acquire several devices for the purposes of the project. The board has been designed as an evaluation board, containing a variety of features at a low price. As a major objective of this study is researching the feasibility of implementing a good PUF, it also makes sense to use the smallest device possible for developing the proof-of-concept solution.

# Our PUF design

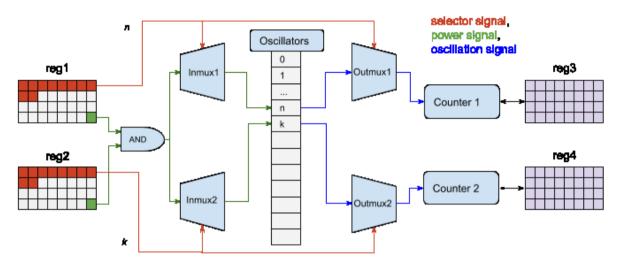

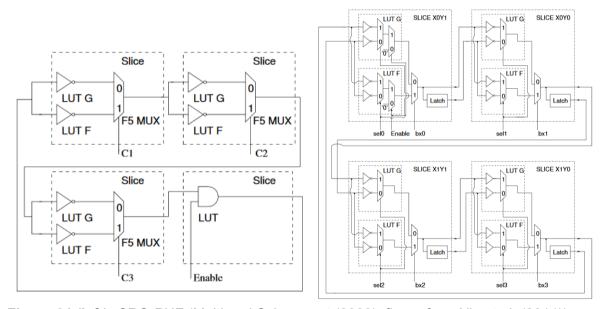

As mentioned, our design is based on the RO-PUF concept with a CPU-based controller program. The controller program has access to four 32-bit registers through an AXI-Lite interface. All the registers are readable and two of the registers are writable by the controller. Registers 1 and 2 are for input; the first ten bits (bits 0-9) of these registers are used as selection bits (RO address). Figure 7 provides a block level visualization of our design, also demonstrating the selection logic. The selection values control which two oscillators are powered up when the power bits are set, and they also control the routing from the same oscillators to the output counters.

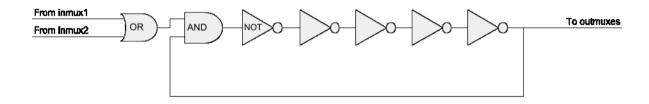

The last bits (bit 31) of the input registers control the power to the PUF. They go through an AND gate before connecting to the signal pin on the input de-multiplexers (inmux1 and inmux2). The purpose of the AND gate is to ensure the oscillation does not start before both registers are written, and power can be turned off with only one register write. Figure 8 demonstrates a ring oscillator. We use an OR gate in front of each oscillator to accommodate two alternative sources for the power signal.

The input registers have 21 unused bits, and these can be used to expand the number of ROs that can be selected. Our design has 1000 ROs, and currently we could select among  $2^{10} = 1024$  units.  $2^{31}$  is so large that it does not impose limits on the practical oscillator count for the design. Registers 3 & 4 are connected to an edge-counting addition block. Each new rising edge of an oscillation arriving to either of the counters increments the connected register by one.

Thus our PUF takes two 10-bit addresses as input and produces two oscillation counts of up to 32 bits as output. However, if we consider the design at a higher level, including the CPU as a part of the PUF, and use the controlling program to perform simple frequency comparisons, the relationship between response and challenge bitstring lengths is

```

Challenge: (K * L * 2) bits Response: K bits Where 0 < K \le N/2 and L = ceil(log2(N))

```

The length of the challenge required is the length of a single address L, multiplied by the number of bits K we want to be in the response, multiplied by 2 because we need to select two oscillators. If we use simple pairwise comparison, K is bounded by N/2. L is the base-2 logarithm of N rounded up. For example, if we have 1000 oscillators, we need 10 address bits:

```

L = ceil(log2(1000)) = ceil(9.97) = 10

```

With 1000 oscillators, the formula results in a 20 bit-challenge for each response bit, meaning 10000 challenge bits are required for the maximum length response of 500 independent bits. The challenge might be procedurally generated to avoid storing it verbatim.

Figure 7: Block design of our RO-PUF

**Figure 8:** Logic-level schematic of our ring oscillator. Each oscillator has an input from each inmux and an output to both outmuxes. A maintained signal on either input makes the output signal oscillate. Frequency has a unique component from manufacturing process variations.

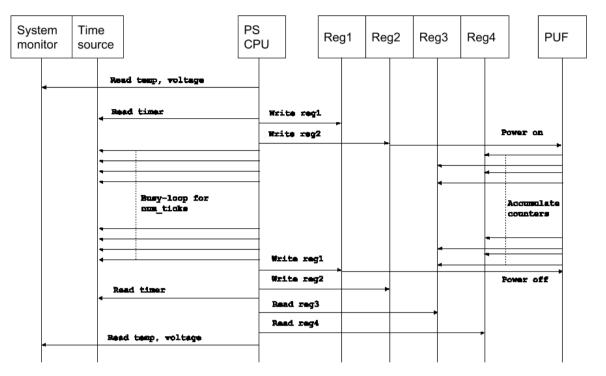

Figure 9: Sequence diagram of a single RO pair measurement.

The order of operations in a pair measurement is shown in figure 9. The measurement is initiated by the CPU by writing to the input registers (reg1 and reg2). While the measurement is running, the rising signal edge (oscillation) counts of the selected oscillators accumulate in the output registers (reg3 and reg4). Meanwhile the controller is continuously sampling the global timer available in the CPU, terminating the run when the elapsed time is longer than the num\_ticks parameter by writing the power bits to zero. Temperature and voltage are read from the system monitor on both sides of the timed block and averaged. Controller program source code is included in the appendix.

| Resource            | # used | # available | % used |

|---------------------|--------|-------------|--------|

| Look-up table (LUT) | 11388  | 14400       | 79.1   |

| LUTRAM              | 72     | 6000        | 1.2    |

| Flip-flop (FF)      | 1558   | 28800       | 5.4    |

**Table 3:** Total resource utilization, including selection and interface logic.

Table 3 presents the FPGA resource utilization of our placed and routed design. The most prevalent components are Look-up tables, which are elements that can be programmed to act as any logical gate: they can map any logic input to any logic output. Flip-flops are essentially single-bit registers that hold any state assigned to them until they are reset. We can see that we have used almost all of the limiting resource (LUTs) on this chip. Further study would be required to achieve an accurate understanding of the scaling behavior of the selection logic (the inmuxes and outmuxes). The counters, the system monitor and the AXI interface do not need to scale and have constant resource requirements.

# Modules

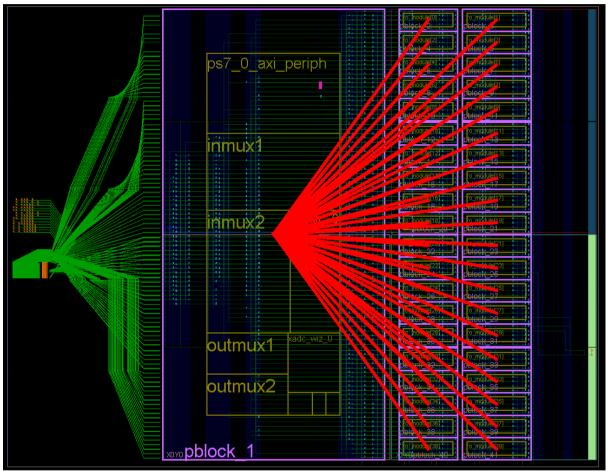

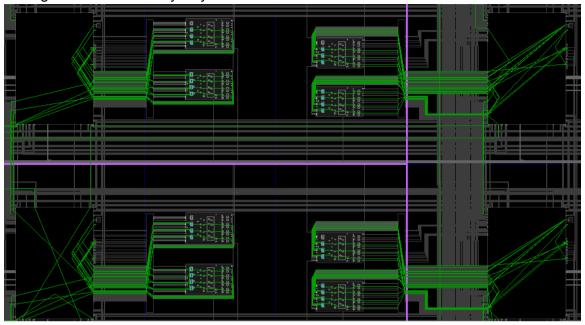

The RO units are divided into modules in order to reduce the effect of systemic variation on the oscillator comparisons (Maiti & Schaumont 2010). As the routing and placing is performed automatically by the Vivado software, we do not know (without performing manual examination after each placing) where exactly each oscillator is placed. The modules allow us, within a certain degree of accuracy depending on module size, to always know where on the chip an oscillator with a certain index (selector address) is located. See Figure 10 to see how the modules were placed on the FPGA.

**Figure 10:** Routing and placement of the design on the Zynq-7000 as represented by the Vivado hardware design suite. The red lines represent "bundle nets" between pblocks. Note the oscillators divided into modules on the right hand side.

## Oscillator selection

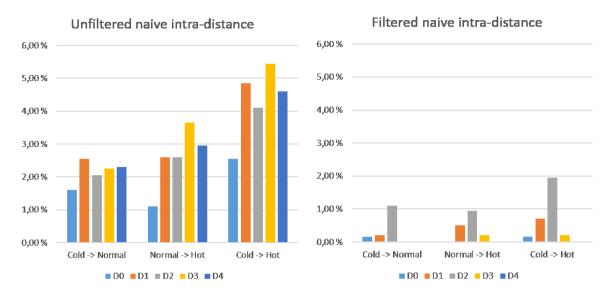

We have implemented three strategies for selecting which oscillators to include in the CRP: the *naive* strategy, the *filtered naive* strategy, and the *Longest Increasing Subsequence Algorithm* (LISA) of Yin & Qu (2010).

# Naive selection

In the *naive* selection scheme, we always select oscillators n and n+1, and encode their relative speed into a single response bit. If oscillation count of n is larger than the oscillation count of n+1, the bit is 1, otherwise 0.

#### Pseudocode:

```

for n from 0 until count_of_oscillators-1; n=n+2

oscs[n], oscs[n+1] = run_oscillators(n,n+1)

if oscs[n] > oscs[n+1]

return 1

else

return 0

```

## Strengths:

In naive selection each bit will be independent, i.e. no oscillator is included in generating more than one response bit, and the relative order of two oscillators can not be inferred from other response bits. As the challenge bitstring is trivial, it reveals no information about the enrolling process. The naive method also avoids systemic chip variation, by 24/25 of the time selecting a pair within the same module and 1/25 of the time from a neighboring module (due to each module containing 25 ROs). If we would e.g. pair the oscillators with lowest absolute values with the largest absolute values, on a biased chip the winning oscillators would all be on one side of the chip, and the response would be biased and predictable.

#### Weaknesses:

The naive method is likely not an optimal way of selecting oscillators. We do not make any effort here to pick particularly good matches from the available population of oscillators, and as such some of the oscillators we select have frequencies inside the random error threshold, and have unstable response bits.

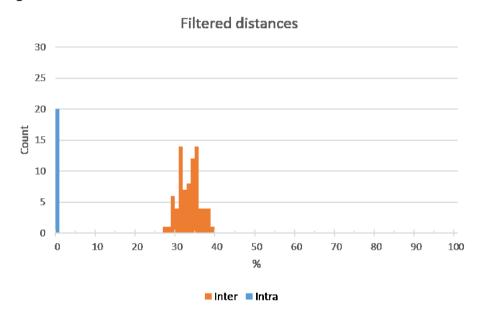

## Filtered naive selection

The *filtered naive* selection scheme works on the same base idea as naive selection, but we filter out all potentially unstable pairs in the enrolling phase.

#### Pseudocode:

```

// do K measurement runs (e.g. with K from 5 to 10), ideally // slightly outside the extremes of the desired operating // temperature range; this should guarantee reliability within that // range while keeping as many bits as possible. for k from 0 until K; k=k+1

```

# Strengths:

Filtered selection should be completely error-free within the environmental parameters of the data used for calibration, and thus achieve perfect reliability within those conditions.

#### Weaknesses:

Filtering eliminates bits from the CRP, likely losing entropy in the process. Filtering is also unpredictable, as we do not know beforehand how many pairs will survive the filter; there might be as many as 95% of bits remaining after the filter, or only 50%.

The result of the filtering is dependent on the calibration data used in the enrolling procedure. Temperature variation during the calibration run is the main factor affecting speed of oscillators in the enrolling data. A large temperature variation within the set of data implies larger variations and more bits will be filtered out, while a too small temperature variation will reduce the reliable operating temperature range of the PUF. Using a dataset with a somewhat larger temperature range than the expected operating temperatures should be used to produce a reliable PUF within the operating range.

As filtering eliminates pairs with the smallest differences, it likely to make the bits of the PUF more predictable, i.e. reduce the inter-distance across devices. This is likely detrimental to the average entropy gained per bit, as intuitively the surviving bits would be more likely to have across-devices bias.

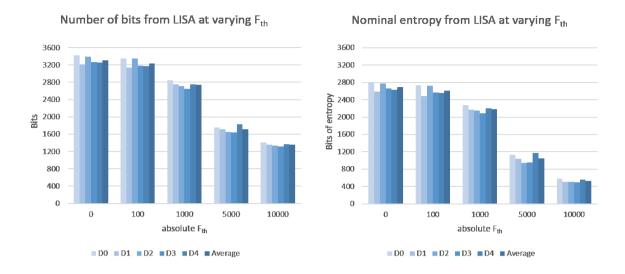

## LISA

LISA stands for Longest Increasing Subsequence Algorithm, presented by Yin & Qu (2010). Yin and Qu reported extracting a maximum of 480 reliable bits from 288 oscillators, thus having an efficiency of n\*1.67. This is much more than the n/2 ratio of bits from normal RO pairing (like our naive selection), of which all bits might not be reliable.

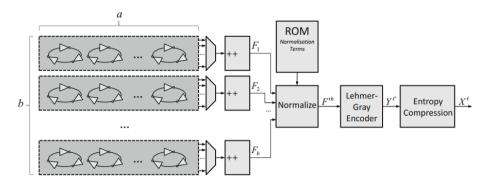

The idea of LISA is to group the RO population into subsequences and encode the information embedded in their mutual order as bits. LISA uses a frequency threshold to define the minimum difference required between two oscillators for them to be permitted in the same subsequence. We use here a Lehmer encoding for denoting order within the subsequences as utilized by Maes et al (2012).

LISA requires the PUF to be controlled. The CRP challenge will also be more complicated, as the controller needs to know precisely which ROs were grouped in which subsequences in the enrollment phase. The mutual order within those subsequences is the secret included in the response. All oscillators will be run and their order evaluated and encoded by the controller.

## **LISA pseudocode** (adapted from Yin & Qu 2010):

```

// "sorted" contains the ROs sorted by their oscillation minima;

// "f th" is the threshold frequency, used as a safety margin

findReliableLIS(List sorted, Int f th)

n = sorted.length

create stack ST 0, push sorted[0] to it

h < - 0

for j <- 1 to n

top <- the top ring osc on stack ST h;

if ((sorted[j].fmin - top.fmin > f_th)

&& (sorted[j]. fmax - top.fmax > f th) )

h++

push sorted[j] to new stack ST h

else

find the stack ST p with the largest index p that has its

top element's fmax smaller than sorted[j].fmax - f th

and fmin smaller than sorted[j].fmin - f th.

if p ! = null

push sorted[j] to ST p+1

return sequence <sorted[j_1], sorted[j_2] ... sorted[j h]> where

sorted[j h] is the top element of ST h

```

#### Strengths:

The response bitstring will no longer be of fixed length, but will vary based on the sequencing performed by LISA. It is also much harder to deconstruct the bit string as after joining the bit-encoded orders together, there is no obvious way of distinguishing which specific oscillator was used to derive which bit.

LISA allows us to extract many more bits from the oscillator frequencies, which likely but not necessarily improves the entropy strength of the response. To estimate the entropy carried, we sum over the set of subsequences

```

H(Y) = sum(log2(b!))

```

where *b* is the length of each subsequence in turn. This provides an entropy upper bound for a bit string built from combining the binary encodings of the relative order of each ring oscillator within its subsequence (Maes et al. 2012). However, this estimate has pitfalls.

#### Weaknesses:

As a single RO pair no longer produces a single bit, the amount of entropy carried by each bit is harder to estimate. Some bits in the binary encodings might be biased; also, while previously a pair yielded a single bit, every RO will produce at least one bit, no matter how biased. In a 2-RO sequence, encoding the order will now yield 1 for the faster RO and 0 for the slower RO. The information carried by a 2-RO sequence is thus exactly the same as previously carried by one pair; however, it is now encoded in two bits. A single-RO sequence always yields 0, and trivially carries no entropy if the attacker knows the sequence lengths, which would be contained as plain text in the challenge.

There are *n!* possible ways to order a sequence (Maes et al. 2012). For this to yield the estimated amount of entropy, the distribution of orderings should be uniformly distributed, which is not the case in reality, as the relative frequencies (at least in our implementation) have bit-specific bias across devices. As such, the formula used by Maes et al. (2012) will only estimate LISA's entropy against an attacker who knows we use LISA, but is ignorant of these biases.

The sequencing process is very sensitive to changes. Minuscule changes in the calibration data can alter the entire sequencing in ways that do not suggest any relation to the old one. This sensitivity will not be a problem in evaluations after the enrolling, as the threshold between frequencies will not be enforced when evaluating the order within the subsequences.

Choice of the threshold frequency will affect both the result of the sequencing and the reliability of the bits. A larger threshold frequency will lead to better reliability, but shorter subsequences and thus fewer bits, and vice versa. A too large threshold will prevent any subsequences from forming, thus collapsing the PUF's entropy output to zero.

# Data collection

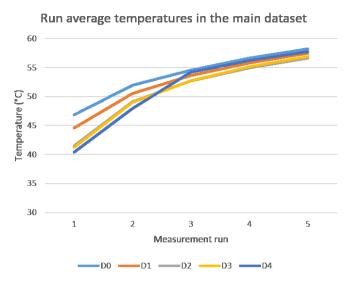

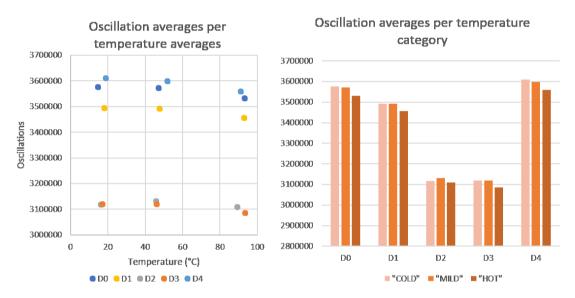

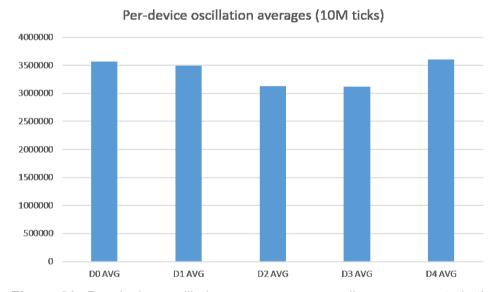

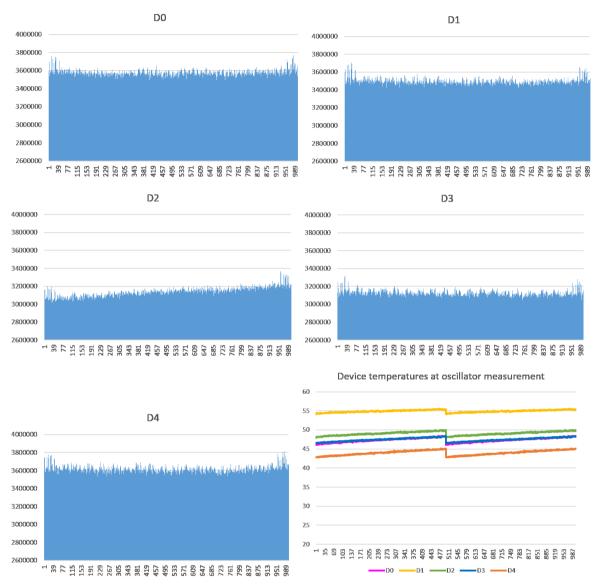

The main dataset was collected from 5 sequential "runs" on each of the 5 devices, with each "run" going through each (n,n+1) RO pair 4 times, for a total of 20 measurements for every oscillator in the dataset. The devices were kept in room temperature before powering on. The chips heated to the starting temperature during powering up and the programming of the FPGA. During the run the increasing chip temperatures in the main dataset are caused by the running PUF. Run length was configured at 10 million CPU cycles per pair, which translates to 15 milliseconds per pair with a CPU clock frequency of approximately 667 MHz (reported as 666 666 687 Hz). Temperature variation within this dataset is presented in figure 11; temperatures ranged from about 40°C to 58°C.

A secondary dataset with high temperature variations was also collected, with a single run performed at each of "cold" (boards pre-cooled in a freezer), "mild" (room temperature) and "hot" (heated with a 90°C hot air blower) environments. Results on this dataset are reported separately when evaluating the error from temperature. In addition, a shorter "jitter dataset" was collected for exploring gaussian random error. Many other runs were performed for controller program testing and other exploratory purposes, but not included in computing the reported statistics. Our controller program output the measurement data in a CSV format, the structure of which is presented in tables 4 and 5.

| Header      | Data type     | Description                                                                                 |  |

|-------------|---------------|---------------------------------------------------------------------------------------------|--|

| DEVICE      | integer       | ID of the test device, manually entered in the terminal before the test run                 |  |

| COUNTER     | unsigned long | Indicates when in the run this RO pair was run                                              |  |

| POSITION    | unsigned      | Indicates the position of this oscillator within the RO pair                                |  |

| RO_INDEX    | unsigned long | The index (address) of the oscillator                                                       |  |

| INCREASE    | unsigned long | The increase in the oscillation counter for this oscillator, read from the output registers |  |

| CPU_TICKS   | unsigned long | Increase of the CPU clock during the run                                                    |  |

| TIME_DELTA  | float         | CPU_TICKS divided by the reported CPU clock frequency                                       |  |

| TEMPERATURE | float         | On-chip (XADC) temperature measurement                                                      |  |

| VCC_INT     | float         | On-chip (XADC) VCC_INT voltage measurement                                                  |  |

| VCC_AUX     | float         | On-chip (XADC) VCC_AUX voltage measurement                                                  |  |

Table 4: CSV output format produced by our controlling program.

```

DEVICE; COUNTER; POSITION; RO_INDEX; INCREASE; CPU_TICKS; TIME_DELTA; TEMPERATURE; VCC_INT; VCC_AUX;

0; 0; 1; 0; 3598563; 10001302; 0.015002; 46.645935; 1.799675; 0.993324;

0; 0; 2; 1; 3668059; 10001302; 0.015002; 46.645935; 1.799675; 0.993324;

0; 1; 1; 2; 3695296; 10001232; 0.015002; 46.680542; 1.799583; 0.993164;

0; 1; 2; 3; 3542482; 10001232; 0.015002; 46.680542; 1.799583; 0.993164;

0; 2; 1; 4; 3556774; 10001224; 0.015002; 46.649780; 1.799698; 0.993118;

0; 2; 2; 5; 3569668; 10001224; 0.015002; 46.649780; 1.799698; 0.993118;

0; 3; 1; 6; 3580311; 10001252; 0.015002; 46.661316; 1.799721; 0.992981;

0; 4; 1; 8; 3603311; 10001252; 0.015002; 46.669006; 1.800064; 0.993050;

0; 4; 2; 9; 3591443; 10001252; 0.015002; 46.669006; 1.800064; 0.993050;

0; 5; 1; 10; 3586012; 10001236; 0.015002; 46.695923; 1.799812; 0.993050;

0; 5; 2; 11; 3760374; 10001236; 0.015002; 46.695923; 1.799812; 0.993050;

0; 6; 1; 12; 3601267; 10001212; 0.015002; 46.695923; 1.799812; 0.993050;

```

**Table 5:** Example CSV output from the beginning of a run, including the header row.

Figure 11: Average temperatures for each device during the main dataset runs.

# Running order

As we aim to understand our error sources, we have reasons to vary the parameters for running each RO pair. In addition to position within the run (as temperature tends to rise towards the end), position within the pair might affect the oscillator frequency. For singling out different error sources, each RO was run four times in each test run, differently ordered:

```

For N from 0 to 999, run (N, N+1)

For N from 999 to 0, run (N, N+1)

For N from 0 to 999, run (N+1, N)

For N from 999 to 0, run (N+1, N)

```

As can be seen, the main dataset always has the ROs paired (n, n+1). To detect if the index of the other RO affects the result, we ran some separate measurements with the configuration

```

For N from 0 to 499, run (N, N+500)

```

As any such effect was not found based on this run, we could stop considering this error.

# Tools and languages

Free versions of Xilinx SDK and Vivado software were used for design and development. Verilog was used as the hardware definition language and C was used as the controller software language. Software was developed using a "standalone" hardware definition, i.e. without any operating system on the board, to minimize dependencies and complexity. Bitstreams (FPGA configuration data) and the PS programs were deployed on the board using Xilinx SDK's "run using system debugger" mode.

The basic elements within each oscillator were placed using "hard macro" constraints. Grouping the oscillators within physically restricted areas on the PL was done using the

pblock functionality in Vivado. The pblock areas were manually designated on the chip, and the design tool placed each oscillator unit within the pblock indicated by its index. Our implemented bitstream contains 40 pblocks containing 25 ring oscillators each for a total of 1000. The modules are as symmetrical as possible, with 5\*5 configurable logic blocks each. We thus know the approximate physical location of each oscillator.

We communicated with the device using a serial connection over USB. The development machine was a Windows 7 PC, with a PuTTY serial communications terminal. Running the PUF was achieved by sending input to the controller program over the serial terminal. Output was collected from the controller program by printing CSV to the terminal, and logging the terminal sessions to file.

Data analysis was performed using Microsoft Excel. LISA was implemented in Python.

# Analysis methods

There are two sides of analysing our PUF: determining how good our PUF is by performing measurements, and analysing the effect of the various sources of undesirable error.

## Measurements

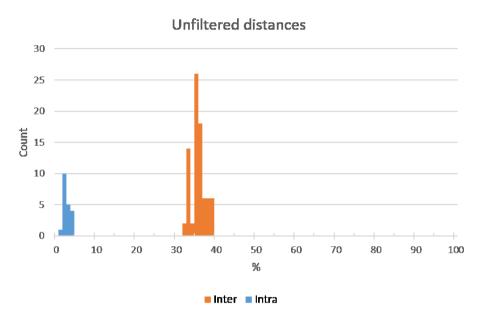

#### Intra-distance and inter-distance

Intra-distance represents what can be called reliability, reproducibility or stability (Suh & Devadas 2007, Maes & Verbauwhede 2010). Intra-distance is the difference within the same device using the same challenge, so it measures bit flips between different runs on the same PUF instances. The ideal intra-distance is 0%. This means no two runs of the same PUF instance with the same challenge flip any of the bits. Thus it is always possible to reproduce the expected response.

Inter-distance represents what has been called uniqueness or unpredictability (Suh & Devadas 2007, Maes & Verbauwhede 2010). Inter-distance is the difference between two PUF instances using the same challenge, so it measures bit flips between devices. The ideal inter-distance is 50%. This means that on average, any two runs on different PUF instances with the same challenge have half of their bits flipped. This indicates perfect unpredictability, on average. The distribution should be inspected to detect outliers.

Both distances are measured as the relative Hamming distance for pairs of responses to same challenge. The relative Hamming distance is simply the number of flipped bits divided by the total number of bits in the bit string.

To achieve better results, both measures are calculated between as many runs and devices as possible. Minimum, maximum and standard deviation are also to be reported (Maes 2013: 97). To estimate the efficiency of the PUF, we report both the raw number of bits, and the estimated entropy carried by those bits as extracted by the various methods.

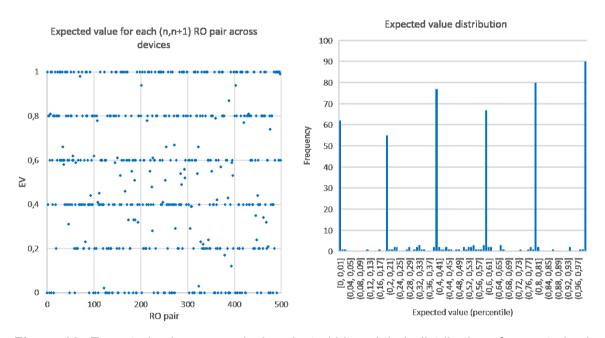

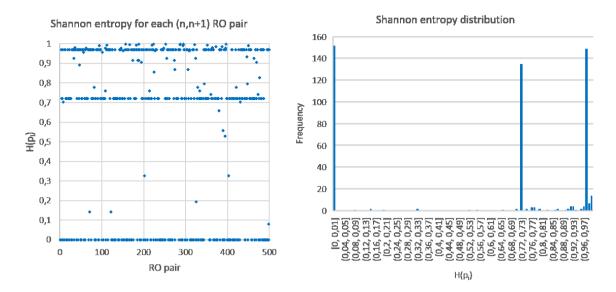

#### **Entropy**

Shannon's entropy can be used to measure the "surprise" i.e. amount of randomness contained in random variables. Cryptography relies heavily on entropy as a measure of the strength of secrets. Entropy is a central measure also in PUF evaluation, as it takes into account the estimated quality of bits in addition to their quantity.

Estimating entropy comes with a number of pitfalls. Most importantly, it should be remembered that entropy calculations are always upper bounds. There might be predictable behavior that is not covered by our estimates, and knowing more about the PUF's behavior will lower the bound for a certain attacker. For an ignorant attacker, the entropy of a PUF response is always trivially equal to the length of the response bitstring (Maes 2013: 109). However, if an attacker can gain more information about the PUF's behavior, the responses can be better predicted and no longer contain as much effective entropy. As such, it is best to consider our entropy calculations to be optimistic estimates.

We will estimate the response entropy for an attacker who has information about bit-specific bias (i.e. measured expected value) across several devices (Maes 2013: 109). This knowledge could realistically be obtained by stealing and analysing a number of instances of our PUF. The entropy carried by a biased bit Y is estimated using the Bernoulli distribution ("unfair coin") formula

$$H(Y) = -\log 2(p) - \log 2(1-p)$$

where p is the probability of the bit being "0", as estimated from the observed expected value (Maes 2013: 109). Sample size affects the accuracy of the estimate.

## Sources of error

#### **Temperature**

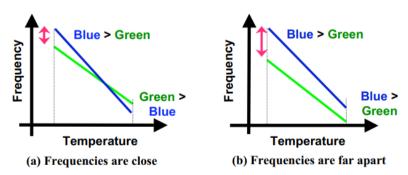

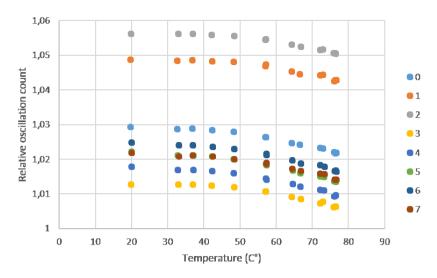

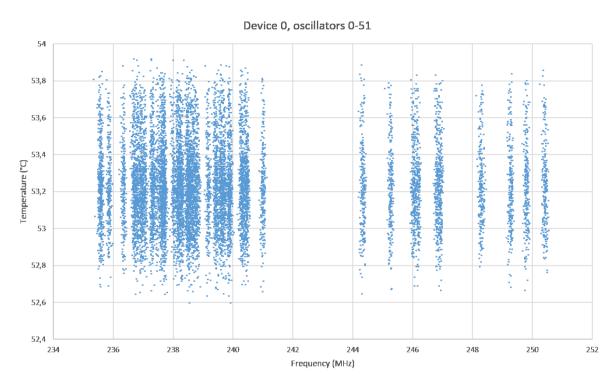

A higher temperature lowers the average frequency of an oscillator. Different RO units react differently and in an unpredictable way, and this might cause bits to flip (illustrated in figure 12). Temperature and voltage were sampled using the on-chip Xilinx Analog-Digital Converter (XADC), a built-in feature of the chip.

**Figure 12:** Temperature changes can cause bit flips when the oscillator frequencies are close, due to the different amplitude of the temperature effect (Suh & Devadas 2007).

The effect of temperature on the stability of our PUF was estimated by collecting a separate dataset, which contains from each device a "cold" measurement taken after cooling the devices in a freezer (on-chip temperatures starting from 6°C and reaching 20°C during the run), a "mild" measurement taken in room temperature (chip temperatures about 50°C), and a "hot" measurement taken with a 90°C a surface-mounted device (SMD) rework tool's hot-

air blower directed at the chip (chip temperatures reaching 90-92°C). The design temperature range of our device is 0-85°C, so extending this range further might cause damage to the device or artefacts resulting from device malfunction.

## Voltage

We did not measure changes in voltage, due to resource constraints. We assume that voltage changes reasonably expected in a normal operating environment have a similar effect as temperature changes, and thus stability can be protected using the same mechanisms, such as filtering. We consider behavior under voltage changes a reliability issue, and not an attack vector.

#### **Aging**

Truly evaluating the effects of long-term operation and aging would require a long timeline and longitudinal study. Additionally, the FPGA fabric in our use-case might spend most of its lifetime in other than PUF use, so the components used for RO units might see wildly differing usage, and thus wear differently than in a lab experiment. We aim to cover our requirements related to aging by considering PUF control mechanisms aimed at early detection of aging deterioration.

# Placing & routing differences

We will not be able to eliminate all routing differences from the design. Rather, we have designed the RO units to be small and modular, each fitting inside a single CLB, where we can reasonably trust that the routings are reasonably design-identical for most of the units. Every CLB has its own routing matrix where the signals of basic elements are connected according to the bitstream. While there is no reason for the synthesis step to make different routings within different CLBs, there are no guarantees with the current design.

The selection logic before the ring oscillators will have significantly varying routing delays. However, if it takes longer for a signal to reach the RO, the shutdown of power should take equally long. Routing of the counters and outmuxes should not be an issue, as these are completely combinatorial (asynchronous) components, and any signal sent by the oscillator will reach the counter register before the PS will be able to read the register.

## Positional difference

Being selected as the "first" or "second" oscillator within the pair might cause effects on the oscillation average. Such effect might be caused by routing delays in the input selectors, and will be investigated.

#### **Delays in the CPU**

The PUF is controlled from the CPU via the input registers. According to the output of the controlling program, there is a non-zero, non-constant delay associated with reading and writing the PUF registers. This is expected to lead to small deviations in run lengths and thus oscillation counts.

## Systemic manufacturing error

As suggested by Maiti & Schaumont (2010) and Zhang et al. (2014), there might exist significant systemic variations in RO speeds both within and between devices. To detect and counter this effect, we have placed the ROs in modules, making their indices to indicate their

approximate physical location on the chip. This allows us to validate the existence of any systemic effects and mitigate their detrimental effects.

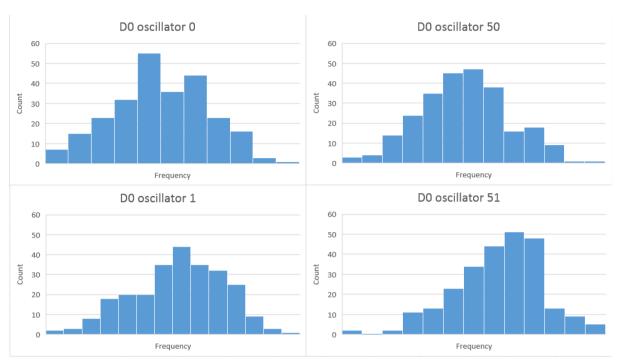

# Gaussian jitter

The output of ring oscillators contains a random component called Gaussian jitter (Valtchanov et al. 2008). Due to the existence of this jitter, there will always be unexplained noise in the RO frequencies, even if we account for all factors that we can influence with our design. A separate dataset was collected to evaluate this error source.

# 5 Evaluation

# Measurements

The measurement results of the naive selection methods are presented in table 6. Results from LISA are not included in this table, as they are not meaningfully comparable. The number of bits and challenge structure in a LISA evaluation are dependent both on the device and the threshold frequency used in the enrolling procedure, making it difficult to compare behavior across devices using these same metrics.

|                                                          | Unfiltered naive | Filtered naive                          |

|----------------------------------------------------------|------------------|-----------------------------------------|

| Relative intra-distance                                  |                  |                                         |

| Average                                                  | 1.97 %           | 0.00 %                                  |

| Min (best case)                                          | 0.60 %           | 0.00 %                                  |

| Max (worst case)                                         | 3.40 %           | 0.00 %                                  |

| Relative inter-distance                                  |                  |                                         |

| Average                                                  | 34.79 %          | 32.60 %                                 |

| Min (worst case)                                         | 31.80 %          | 26.69 %                                 |

| Max (best case)                                          | 38.20 %          | 38.02 %                                 |

| Average output bits                                      | n/2 = 500 bits   | n/2*85.76 %<br>~= 429 bits              |

| Average entropy when attacker knows bit-specific bias    | 295 bits         | 295*85.76%<br>~= 253 bits <sup>(1</sup> |

| Average bits of entropy per output bit (entropy density) | 0.59             | 0.51                                    |

<sup>(1:</sup> assumes all bits filtered out are non-zero-entropy bits, that provide the expected entropy of a non-zero-entropy bit; in other words, a reasonable worst case assumption.

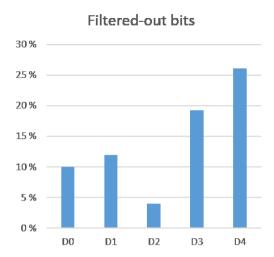

**Table 6:** Measures from our enrolling methods.