# ANALOG BASEBAND CIRCUITS FOR SENSOR SYSTEMS

**Doctoral Dissertation**

Jere Järvinen

Helsinki University of Technology Faculty of Electronics, Communications and Automation Department of Micro and Nanosciences

## ANALOG BASEBAND CIRCUITS FOR SENSOR SYSTEMS

**Doctoral Dissertation**

Jere Järvinen

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Faculty of Electronics, Communications and Automation for public examination and debate in Auditorium S1 at Helsinki University of Technology (Espoo, Finland) on the 16th of May, 2008, at 12 noon.

Helsinki University of Technology Faculty of Electronics, Communications and Automation Department of Micro and Nanosciences

Teknillinen korkeakoulu Elektroniikan, tietoliikenteen ja automaation tiedekunta Mikro- ja nanotekniikan laitos Distribution:

Helsinki University of Technology

Faculty of Electronics, Communications and Automation

Department of Micro and Nanosciences

P.O. Box 3000

FI - 02015 TKK

**FINLAND**

URL: http://www.ecdl.tkk.fi/

Tel. +358-9-451 2271 Fax +358-9-451 2269

E-mail: jere.jarvinen@iki.fi

© 2008 Jere Järvinen

ISBN 978-951-22-9364-3

ISBN 978-951-22-9365-0 (PDF)

ISSN 1795-2239

ISSN 1795-4584 (PDF)

URL: http://lib.tkk.fi/Diss/2008/isbn9789512293650/

TKK-DISS-2468

Multiprint Oy

Espoo 2008

| ABSTRACT OF DOCTORAL DISSERTATION                       | HELSINKI UNIVERSITY OF TECHNOLOGY P.O. BOX 1000, FI-02015 TKK http://www.tkk.fi |

|---------------------------------------------------------|---------------------------------------------------------------------------------|

| Author                                                  |                                                                                 |

| Name of the dissertation                                |                                                                                 |

|                                                         |                                                                                 |

| Manuscript submitted                                    | Manuscript revised                                                              |

| Date of the defence                                     |                                                                                 |

| Monograph                                               | Article dissertation (summary + original articles)                              |

| Faculty                                                 |                                                                                 |

| Department                                              |                                                                                 |

| Field of research                                       |                                                                                 |

| Opponent(s)                                             |                                                                                 |

| Supervisor                                              |                                                                                 |

| Instructor                                              |                                                                                 |

| Abstract                                                |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

|                                                         |                                                                                 |

| Keywords                                                |                                                                                 |

| ISBN (printed)                                          | ISSN (printed)                                                                  |

| ISBN (pdf)                                              | ISSN (pdf)                                                                      |

| Language                                                | Number of pages                                                                 |

| Publisher                                               |                                                                                 |

| Print distribution                                      |                                                                                 |

| The dissertation can be read at http://lib.tkk.fi/Diss/ |                                                                                 |

| VÄITÖSKIRJAN TIIVISTELMÄ                                 | TEKNILLINEN KORKEAKOULU PL 1000, 02015 TKK http://www.tkk.fi |  |  |

|----------------------------------------------------------|--------------------------------------------------------------|--|--|

| Tekijä                                                   |                                                              |  |  |

| Väitöskirjan nimi                                        |                                                              |  |  |

|                                                          |                                                              |  |  |

| Käsikirjoituksen päivämäärä                              | Korjatun käsikirjoituksen päivämäärä                         |  |  |

| Väitöstilaisuuden ajankohta                              |                                                              |  |  |

| Monografia                                               | Yhdistelmäväitöskirja (yhteenveto + erillisartikkelit)       |  |  |

| Tiedekunta                                               |                                                              |  |  |

| Laitos                                                   |                                                              |  |  |

| Tutkimusala                                              |                                                              |  |  |

| Vastaväittäjä(t)                                         |                                                              |  |  |

| Työn valvoja                                             |                                                              |  |  |

| Työn ohjaaja                                             |                                                              |  |  |

| Tiivistelmä                                              |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

|                                                          |                                                              |  |  |

| Asiasanat                                                | T                                                            |  |  |

| ISBN (painettu)                                          | ISSN (painettu)                                              |  |  |

| ISBN (pdf)                                               | ISSN (pdf)                                                   |  |  |

| Kieli                                                    | Sivumäärä                                                    |  |  |

| Julkaisija                                               |                                                              |  |  |

| Painetun väitöskirjan jakelu                             |                                                              |  |  |

| Luettavissa verkossa osoitteessa http://lib.tkk.fi/Diss/ |                                                              |  |  |

## **Preface**

The research for this thesis was carried out at the Electronic Circuit Design Laboratory of the Helsinki University of Technology during the period 2002-2006. The research was supported by the Nokia Research Center, VTI Technologies, and the Finnish Funding Agency for Technology and Innovation (TEKES). I would also like to thank the Ulla Tuominen Foundation and the Jenny and Antti Wihuri Foundation for their support.

I want to thank my supervisor Professor Kari Halonen for giving me the opportunity to work in the laboratory among very many talented design engineers. Professor Halonen provided me a unique opportunity to work on what are the most challenging and interesting current research topics. The reviewers of this thesis, Kimmo Koli, D.Sc. from ST Microelectronics, Finland, and Professor Svante Signell from the Royal Institute of Technology, Sweden, also deserve warm thanks for their comments and suggestions.

I thank all my former colleagues at the Electronic Circuit Design Laboratory for the many great memories I'm left with from the past eight years since I started to work as a research assistant in the laboratory. First of all, I want to thank Jussi Pirkkalaniemi, my friend and colleague from the beginning of my studies at Helsinki University of Technology. I want also to thank my team members during these studies. Jarkko Jussila, D.Sc. deserves thanks for the many valuable things he taught me. Professor Jussi Ryynänen also deserves thanks for taking care of the project management and giving valuable advice over the past five years or so. Jouni Kaukovuori deserves my special thanks for his great co-operation in various projects. I have really enjoyed our teamwork. Mika Kämäräinen, Matti Paavola, Mika Laiho, D.Sc. and Mikko Saukoski, D.Sc., you were a great team to work with. I want especially to thank Mikko Saukoski for many interesting discussions and for pushing me to give my best.

For the great laboratory spirit I want to thank in particular Väinö Hakkarainen, Lauri Koskinen, Pikkis, Harri Pellikka, Artturi Kaila, Ville Saari, Mikko Hotti, Jonne Lindeberg, Mikko Kaltiokallio, Mikko Kärkkäinen, Mikko Talonen, Mikko Varonen, Lauri Sumanen, Saska Lindfors, Teemu Salo and Mika Länsirinne. I also want to thank Helena Yllö for the most enjoyable coffee room company and for keeping the laboratory working.

Of course, there has to be some balance between work and leisure. Therefore, I would like to thank my brother Juho and my dear friends Toni, Rami, Antti and Riku for all the free-time activities we have enjoyed during these years.

I am so grateful for the help given to me by my father Klaus Järvinen† and my mother Marjo Järvinen. Your love and support have brought me this far. I also wish to thank my grandparents Dagny Järvinen, Maija and Heikki Miettinen for believing in me. My parents-in-law Raili and Juha Hämäläinen are acknowledged for taking part in our family's life, not forgetting the great Sunday meals.

Finally, I would like to thank my beloved wife Tanja. Without your love this road would have been rocky and lonely. I want also to thank you for our lovely children Jasmin and Alex, who have brought so much happiness to my life.

Espoo, May 2008

Jere Järvinen

## **Contents**

|   | Abs  | tract    |                                          | İ    |

|---|------|----------|------------------------------------------|------|

|   | Tiiv | istelmä  |                                          | iii  |

|   | Pref | ace      |                                          | v    |

|   | Con  | tents    |                                          | vii  |

|   | List | of pub   | lications                                | xi   |

|   | Con  | tributio | on of the author                         | xiii |

|   | Sym  | ıbols an | ad abbreviations                         | xv   |

| 1 | Intr | oductio  | on                                       | 1    |

|   | 1.1  | Motiv    | ation for the Thesis                     | 1    |

|   | 1.2  | Analo    | g Circuit Design in Deep Sub-Micron CMOS | 2    |

|   | 1.3  | Resear   | rch Contribution                         | 3    |

|   | 1.4  | Organ    | ization of the Thesis                    | 4    |

| 2 | Base | eband (  | Circuits for Wireless Sensors            | 5    |

|   | 2.1  | Gener    | al                                       | 5    |

|   | 2.2  | Specif   | Circuits                                 | 6    |

|   |      | 2.2.1    | Noise Figure and Baseband Noise          | 7    |

|   |      | 2.2.2    | Linearity                                | 7    |

|   |      | 2.2.3    | Duty Cycle                               | 9    |

|   |      | 2.2.4    | Group Delay and AM-to-PM conversion      | 10   |

|   |      | 2.2.5    | Start-up Time                            | 10   |

|   |      | 2.2.6    | Filter Performance Comparison            | 10   |

|   | 2.3  | Senso    | r Baseband Circuits                      | 11   |

|   |      | 2.3.1    | Mixer-Baseband Interface                 | 11   |

|   |     | 2.3.2    | Continuo   | ous-Time Active Filters                               | 13 |

|---|-----|----------|------------|-------------------------------------------------------|----|

|   |     |          | 2.3.2.1    | Active-RC                                             | 13 |

|   |     |          | 2.3.2.2    | g <sub>m</sub> -C                                     | 15 |

|   |     |          | 2.3.2.3    | All-MOS $g_m$ -C Filter                               | 16 |

|   |     |          | 2.3.2.4    | Comparison of Active-RC and $g_m$ -C Filters          | 20 |

|   |     | 2.3.3    | Limiter a  | and Received Signal Strength Indicator                | 20 |

|   |     |          | 2.3.3.1    | DC Offset Compensation Techniques for Limiters .      | 21 |

|   |     |          | 2.3.3.2    | Limiter Gain and Bandwidth                            | 25 |

| 3 | Δna | log_to_T | Digital Co | nverters for Sensor Applications                      | 27 |

| J | 3.1 | _        | _          |                                                       | 27 |

|   | 3.2 |          |            | r A/D Converters                                      | 28 |

|   | 3.2 | 3.2.1    |            | ecifications                                          | 28 |

|   |     | 3.2.2    |            | Specifications                                        | 29 |

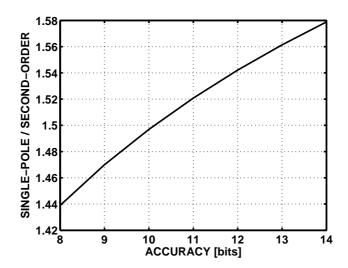

|   |     | 3.2.3    | •          | werter Performance Comparison                         | 31 |

|   | 3.3 |          |            | for Switched-Capacitor Circuits                       | 32 |

|   | 3.3 | 3.3.1    | •          | nal Amplifiers                                        | 32 |

|   |     | 3.3.1    | 3.3.1.1    | Operational Amplifier Properties                      | 32 |

|   |     |          | 3.3.1.2    | Single-Stage Operational Amplifiers                   | 33 |

|   |     |          | 3.3.1.3    | Two-Stage Operational Amplifiers                      | 34 |

|   |     | 3.3.2    |            | Comparators                                           | 37 |

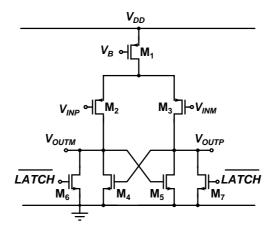

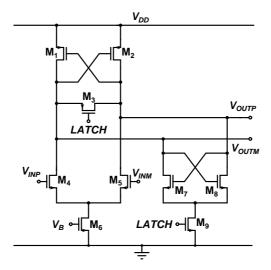

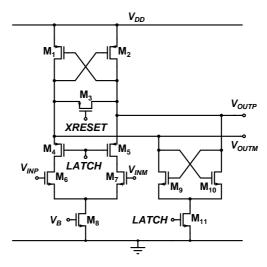

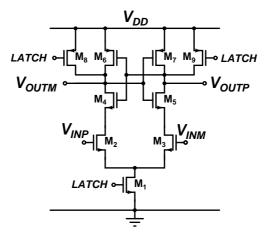

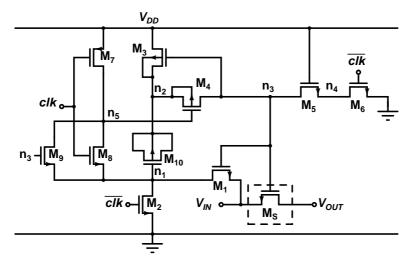

|   |     | 3.3.2    | 3.3.2.1    | Static Latched Comparators                            | 38 |

|   |     |          | 3.3.2.2    | Class AB Latched Comparators                          | 39 |

|   |     |          | 3.3.2.3    | Dynamic Latched Comparators                           | 40 |

|   |     |          | 3.3.2.4    | Preamplifier for Latched Comparators                  | 41 |

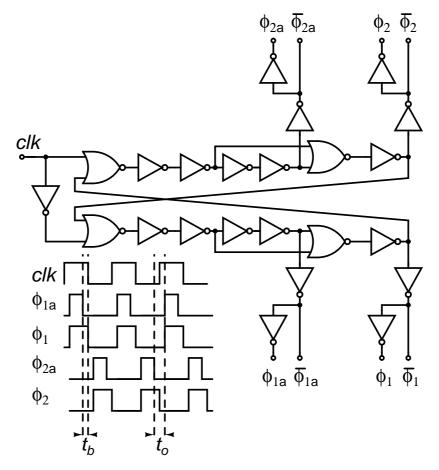

|   |     | 3.3.3    |            | eneration                                             | 42 |

|   |     | 3.3.4    |            | Ceircuits                                             | 44 |

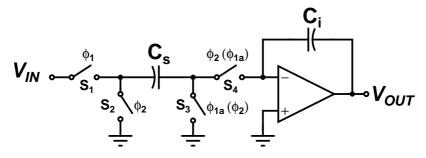

|   |     | 3.3.1    | 3.3.4.1    | SC Integrator                                         | 44 |

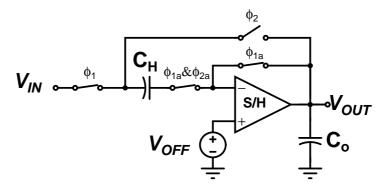

|   |     |          | 3.3.4.2    | Sample and Hold                                       | 44 |

|   |     | 3.3.5    |            | ading                                                 | 46 |

|   |     | 3.3.6    |            | tling Requirements                                    | 48 |

|   | 3.4 |          |            | itched-Capacitor Circuits                             | 50 |

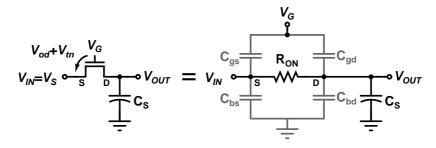

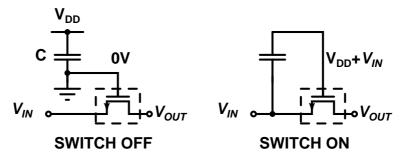

|   | 3.1 | 3.4.1    |            | witch Transistor Properties in SC Circuits            | 50 |

|   |     | 3.4.2    |            | SC Circuits                                           | 53 |

|   |     | 3.1.2    | 3.4.2.1    | Noise in SC Integrator                                | 54 |

|   |     |          | 3.4.2.2    | Noise in SC S/H Circuit                               | 55 |

|   | 3.5 | ΛΣ. Μα   |            | /D Converters                                         | 56 |

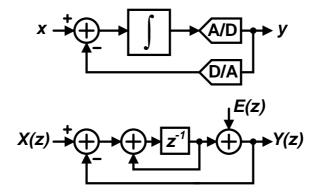

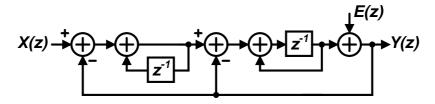

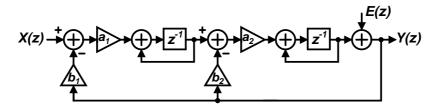

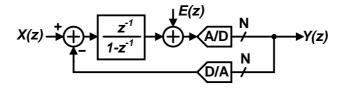

|   | 5.5 | 3.5.1    |            | paping in $\Delta\Sigma$ Modulators                   | 57 |

|   |     | 3.5.2    |            | ct of Operational Amplifier Finite Gain and Settling. | 59 |

|   |     | 0.0.2    | I II LIIC  |                                                       |    |

| 5 | Con | clusions | 3                                                                        | 83 |

|---|-----|----------|--------------------------------------------------------------------------|----|

| 4 | Sum | mary o   | f publications                                                           | 79 |

|   |     | 3.6.6    | Other Algorithmic A/D Converters                                         | 77 |

|   |     | 3.6.5    | Algorithmic A/D Converters using Current-Mode Approach .                 | 76 |

|   |     | 3.6.4    | Algorithmic A/D Converters with Digital Correction                       | 74 |

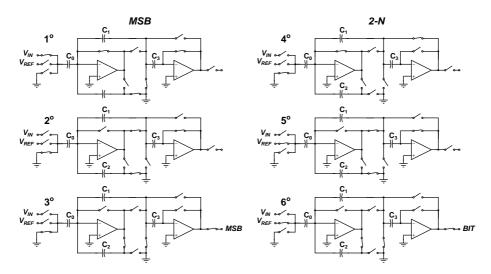

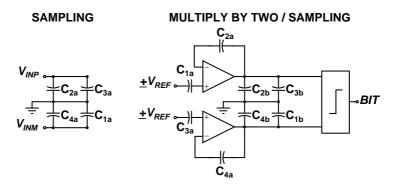

|   |     | 3.6.3    | Capacitance Ratio-Independent Principle                                  | 68 |

|   |     | 3.6.2    | The Effect of Operational Amplifier Finite Gain and Settling .           | 67 |

|   |     | 3.6.1    | Algorithmic A/D Converter Speed Requirements                             | 67 |

|   | 3.6 | Algori   | thmic A/D Converters                                                     | 66 |

|   |     | 3.5.5    | $\Delta\Sigma$ Modulators for GSM and WCDMA $\ \ldots \ \ldots \ \ldots$ | 64 |

|   |     | 3.5.4    | Discrete-Time vs. Continuous-Time $\Delta\Sigma$ Modulators              | 64 |

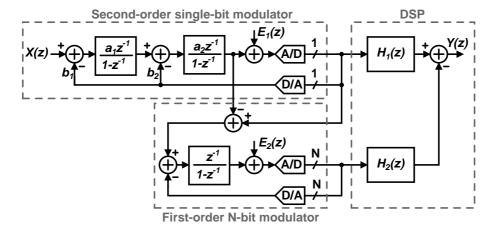

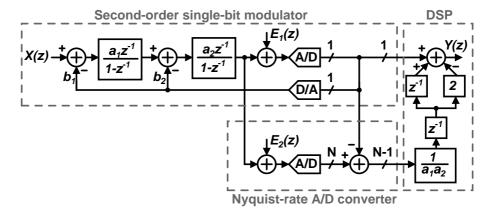

|   |     |          | 3.5.3.2 Multi-Stage $\Delta\Sigma$ Modulator Topologies                  | 62 |

|   |     |          | 3.5.3.1 Multi-Bit $\Delta\Sigma$ Modulator Topologies                    | 61 |

|   |     | 3.5.3    | $\Delta\Sigma$ Modulator Topologies                                      | 61 |

|   |     |          |                                                                          |    |

## List of publications

- [P1] J. A. M. Järvinen, J. Kaukovuori, J. Ryynänen, J. Jussila, K. Kivekäs, M. Honkanen, and K. A. I. Halonen, "2.4-GHz receiver for sensor applications," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 7, pp. 1426–1433, July 2005.

- [P2] J. Kaukovuori, J. A. M. Järvinen, J. Ryynänen, J. Jussila, K. Kivekäs, and K. A. I. Halonen, "Direct-conversion receiver for ubiquitous communications," in *Proc. IEEE Radio and Wireless Symposium*, 17-19 Jan. 2006, pp. 103–106.

- [P3] J. Järvinen and K. Halonen, "A 1.2V dual-mode GSM/WCDMA  $\Delta\Sigma$  modulator in 65nm CMOS," in *Proc. IEEE International Solid-State Circuits Conference, Digest of Technical Papers*, 5-9 Feb. 2006, pp. 488–489.

- [P4] J. A. M. Järvinen, M. Saukoski, and K. Halonen, "A 12-bit 32µW ratio-independent algorithmic ADC," in *Proc. Symposium on VLSI Circuits*, 15-17 June 2006, pp. 58–59.

- [P5] M. Paavola, M. Kämäräinen, J. A. M. Järvinen, M. Saukoski, M. Laiho, and K. A. I. Halonen, "A 62µA interface ASIC for a capacitive 3-axis microaccelerometer," in *IEEE Journal of Solid-State Circuits*, vol. 42, no. 12, Dec. 2007, pp. 2651–2665.

- [P6] J. A. M. Järvinen, M. Saukoski, and K. Halonen, "A 12-bit ratio-independent algorithmic A/D converter for a capacitive sensor interface," in *IEEE Transactions on Circuits and Systems I*, vol. 55, no. 4, Apr. 2008, accepted for publication.

## Contribution of the author

#### [P1] 2.4-GHz Receiver for Sensor Applications

The receiver was designed, implemented, and measured by a research team which consisted of four members, including the author. The other members were Prof. J. Ryynänen, Mr. J. Kaukovuori, and D.Sc J. Jussila. The author is responsible for the design and implementation of the baseband circuits together with D.Sc J. Jussila. The measurements were made together with Mr. J. Kaukovuori, who was responsible for the design and implementation of the radio frequency (RF) front-end together with Prof. J. Ryynänen. The writing of the manuscript was done by the whole research team together. The other authors, D.Sc K. Kivekäs and Mr. M. Honkanen, are mainly responsible for writing about details conserning the sensor system. Prof. K. Halonen made valuable comments on the manuscript. The circuit was originally published in [1]

#### [P2] Direct-conversion Receiver for Ubiquitous Communications

This paper is an improved version of [P1]. As in [P1], the author is responsible for the design and implementation of the baseband circuits together with D.Sc J. Jussila, who had the main design responsibility for the limiting amplifier and current reference designs. The measurements were made together with Mr. J. Kaukovuori. The writing of the manuscript was done by the whole research team together. Prof. K. Halonen made valuable comments on the manuscript.

#### [P3] A 1.2V Dual-Mode GSM/WCDMA ΔΣ Modulator in 65nm CMOS

The author was responsible for all the work regarding this paper. Prof. K. Halonen supervised the author and made valuable comments on the manuscript.

#### [P4] A 12-bit 32µW Ratio-Independent Algorithmic ADC

The author is responsible for the design and implementation of the analog-to-digital (A/D) converter topology. The writing of the manuscript and the design of the dynamically biased operational amplifier were performed in co-operation with Mr. M. Saukoski. Prof. K. Halonen made valuable comments on the manuscript.

#### [P5] A 62µA Interface ASIC for a Capacitive Three-Axis Microaccelerometer

The interface ASIC was designed, implemented, and measured by a research team which consisted of five members, including the author. The other team members were Lic.Sc M. Paavola, Lic.Sc M. Kämäräinen, Mr. M. Saukoski, and D.Sc M. Laiho. The author is responsible for the design and implementation of the A/D converter. Lic.Sc M. Paavola designed the clock generators and voltage, current, and temperature references under the supervision of D.Sc M. Laiho and Mr. M. Saukoski. Lic.Sc M. Kämäräinen was responsible for the design of the capacitive sensor front-end under the supervision of Mr. M. Saukoski. Mr. M. Saukoski also contributed to the system level design and, with the author, co-designed the dynamic amplifiers for the A/D converters. The writing of the manuscript was done by the whole research team together. Prof. K. Halonen made valuable comments on the manuscript. The whole system was originally published in [2] and the designed A/D converter is published separately in [P6,3].

## [P6] A 12-bit Ratio-Independent Algorithmic A/D Converter for a Capacitive Sensor Interface

This is a more detailed description of the A/D converter presented in [P5,3]. As in [P4], the author is responsible for the design and implementation of the A/D converter. The author designed the dynamically biased operational amplifier in co-operation with Mr. M. Saukoski. The writing of the manuscript was done together with Mr. M. Saukoski. Prof. K. Halonen made valuable comments on the manuscript.

## Symbols and abbreviations

β Feedback factor

$\Delta V_G$  Voltage change at the transistor gate

$\Delta\Sigma$  Delta-Sigma

γ MOS transistor process-dependent noise excess factor

∞ Infinity

$\mu_n$  NMOS transistor carrier mobility

$\mu_p$  PMOS transistor carrier mobility

$\omega_c$  Gain stage corner frequency

$\omega_n$  Pole frequency

$\omega_{1,2}$  Two-tone test signal frequencies

$\omega_{bb}$  Baseband passband edge corner frequency

$\omega_{FB}$  —3-dB corner frequency of the feedback loop

$\overline{\phi_{1,2}}$  Inverted clock phases

$\overline{\phi_{1a,2a}}$  Advanced inverted clock phases

*clk* Inverted clock signal

$\phi_{1,2}$  Clock phases

$\phi_{1a,2a}$  Advanced clock phases

τ Settling time constant

$\xi$  Damping factor

A Area

$f_s$

| A(s)         | Amplifier transfer function in s-domain                   |

|--------------|-----------------------------------------------------------|

| $A_0$        | Amplifier gain at zero frequency                          |

| $a_0$        | DC gain of low-pass second-order system transfer function |

| $A_F(s)$     | Transfer function of an amplifier in a feedback loop      |

| $A_s$        | Gain stage gain at zero frequency                         |

| $A_{0,tran}$ | Limiter transient gain at zero frequency                  |

| $a_{1,2}$    | Integrator gain coefficients                              |

| $A_{FB}$     | DC gain of the feedback loop                              |

| $A_{LP}(s)$  | Transfer function of a low-pass second-order system       |

| $A_{MAX}$    | Maximum transient gain                                    |

| $A_{tot}$    | Total gain of <i>M</i> -stage cascade                     |

| $b_{1,2}$    | Feedback scaling coefficients                             |

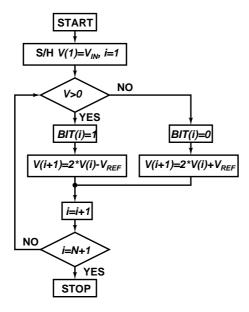

| BIT(i)       | Bit on the $i_{th}$ cycle                                 |

| clk          | Clock signal                                              |

| D            | Duty cycle                                                |

| DNL          | Differential nonlinearity                                 |

| DR           | Dynamic range                                             |

| e            | Quantization error                                        |

| E(z)         | Quantization error in z-domain                            |

| $E^2(f)$     | Quantization noise power spectral density                 |

| $e_n^2$      | MOS transistor noise mean square value                    |

| $e_{rms}^2$  | Quantization error mean square value                      |

| ENOB         | Effective number of bits                                  |

| f            | Frequency                                                 |

|              |                                                           |

Sampling frequency

*f*<sub>bb</sub> Baseband bandwidth

f<sub>bw</sub> Signal bandwidth

$f_{clk}$  Clock frequency

$f_{IN}$  Input signal frequency

$FOM_A$  Area figure of merit

$FOM_F$  Filter figure of merit

$FOM_P$  Power figure of merit

$FOM_{PA}$  Figure of merit including both power and area

G Passband gain

$g_m$  Transistor transconductance

g<sub>ds</sub> Transistor drain-source conductance

Gain-bandwidth product

H(f) Brick wall filter response

$H_{1,2}(z)$  Digital filters in z-domain

$H_{AC}(s)$  AC coupling transfer function

$H_{casc}(s)$  Transfer function of cascaded gain stages

$H_{FB}(s)$  Feedback loop transfer function

$H_S(s)$  Total DC feedback loop transfer function

*i* Number of the cycle

*I<sub>B</sub>* Bias current

*I*<sub>D</sub> Drain current

$I_{1,2}$  Signal currents

*I<sub>IN</sub>* Input signal current

*I<sub>OUT</sub>* Output signal current

*I<sub>slew</sub>* Operation amplifier slewing current

$I_{supply}$  Current from power supply

*ICP* Input compression point

IIP2 Second-order input intercept point

IIP3 Third-order input intercept point

IMD Intermodulation distortion

INL Integral nonlinearity

k Boltzmann constant

$k_0$  DC offset coefficient

*k*<sub>1</sub> Linear gain coefficient

$k_2, k_3, \dots, k_n$  Nonlinearity coefficients

KF Process-dependent MOS transistor flicker noise parame-

ter

L MOS transistor gate length

*L* Order of  $\Delta\Sigma$  modulator loop filter

$L_{ov}$  MOS transistor channel overlap of the drain/source re-

gions

LSB Least significant bit

M Number of cascaded gain stages

MSB Most significant bit

Number of digitized bits

$n_{bw}^2$  Noise power in the signal band

$n_{thermal}^2$  Sampled thermal noise power

$N_{steps}$  Maximum number of operation steps per bit

*NF* Noise figure

$NF_{RF}$  Front-end noise figure

$NF_{RX}$  Receiver noise figure

NTF(z) Noise transfer function in z-domain

OCP Output compression point

OIP2 Second-order output intercept point

OIP3 Third-order output intercept point

Order Filter order

OSR Oversampling ratio

$p_1$  Single-pole frequency

*p*<sub>2</sub> Non-dominant pole frequency

*P*<sub>D</sub> Power dissipation

$P_{1dB}$  1-dB compression point

$P_{casc}$  Total power dissipation of cascaded gain stages

$P_{IMD2.IN}$  Second-order *IMD* component at the input

$P_{IMD3,IN}$  Third-order *IMD* component at the input

$P_{IN}$  Input power

$P_{OUT}$  Output power

Q Pole quality factor

$Q_C$  Charge in capacitor C

$Q_{ch}$  MOS switch transistor channel charge

S Settling accuracy

SFDR Spurious-free dynamic range

SNDR Signal-to-noise and distortion ratio

SNR Signal-to-noise ratio

STF(z) Signal transfer function in z-domain

T Absolute temperature

t Time

*t<sub>b</sub>* Delay required to implement bottom plate sampling

$t_o$  Delay between the non-overlapping clock signals

$T_s$  Settling time

$t_{duty}$  Duration that the output signal is non-zero

T<sub>period</sub> Signal period

V Test signal amplitude

V(i) Voltage signal on the  $i_{th}$  cycle

$v_C^2$  Total thermal noise mean-squared value sampled to ca-

pacitor C

$v_{n,opamp}^2$  Total thermal noise mean-squared value of the opera-

tional amplifier

$V_{sine.rms}^2$  Sine wave mean square value

$V_{R}$  Bias voltage

$V_G$  Transistor gate voltage

$V_{CMFB}$  Common-mode feedback voltage

$V_{ctrl}$  Transistor gate control voltage

$V_{DD}$  Supply voltage

$v_{ds.sat}$  Transistor drain-source saturation voltage

$V_{FS}$  Full-scale voltage input range

$V_{GS}$  MOS transistor gate-source voltage

$V_{IMD2}$  Second-order intermodulation distortion

$V_{IMD3}$  Third-order intermodulation distortion

$V_{IN,min}$  Minimum input signal voltage

$V_{INM}$  Negative input signal voltage

$V_{INP}$  Positive input signal voltage

$V_{IN}$  Input signal voltage

$V_{LSB}$  Quantization step size

$v_{n.out.BB}$  Noise voltage density at the baseband output

$V_{od}$  MOS transistor gate overdrive voltage

$V_{OFF}$  Offset voltage

$V_{OUTM}$  Negative output signal voltage

$V_{OUTP}$  Positive output signal voltage

$V_{OUT}$  Output signal voltage

$V_{REF}$  Reference voltage

$V_{SIG}$  Signal amplitude

$V_S$  MOS transistor source voltage

$V_{tn}$  NMOS transistor threshold voltage

W MOS transistor gate width

X(z) Input signal in z-domain

Y(z) Output signal in z-domain

3G Third generation

A/D Analog-to-digital

AC Alternating current

Active-RC Filter technique that uses resistors, capacitors, and oper-

ational amplifiers

ADC Analog-to-digital converter

AGC Automatic gain control

AM-to-PM Amplitude variation to phase deviation

ASIC Application-specific integrated circuit

BB Baseband

BiCMOS Bipolar CMOS

C Capacitor

C<sub>bd</sub> MOS transistor channel-to-bulk and junction capacitance

at drain

C<sub>bs</sub> MOS transistor channel-to-bulk and junction capacitance

at source

C<sub>C</sub> Pole-splitting capacitor

C<sub>eff</sub> Effective load capacitance

C<sub>gd</sub> MOS transistor gate-to-drain and gate-to-channel capac-

itance

$C_{gs}$  MOS transistor gate-to-source and gate-to-channel ca-

pacitance

C<sub>H</sub> Sample-and-hold capacitor

C<sub>in</sub> Total OTA input capacitance

C<sub>i</sub> Integrating capacitor

C<sub>L</sub> Total load capacitance, load capacitor

C<sub>n1</sub> Parasitic capacitance at node n1

C<sub>ov</sub> MOS transistor overlap capacitance

Cox MOS transistor gate oxide capacitance

C<sub>o</sub> Total OTA output capacitance

C<sub>s</sub> Sampling capacitor

CDS Correlated double sampling

CMFB Common-mode feedback

CMFF Common-mode feed-forward

CMOS Complementary metal oxide semiconductor

CT Continuous-time

D/A Digital-to-analog

DC Direct current

DEM Dynamic element matching

DLL Delay locked loop

DSP Digital signal processor

DT Discrete-time

FSK Frequency-shift keying

g<sub>m</sub>-C Filter technique that uses transconductors and capacitors

g<sub>m</sub>-C-OTA Filter technique that uses transconductors, capacitors, and

**OTAs**

GPRS General packet radio service

GSM Global system for mobile communication

ISM Industrial, scientific and medical

K Current-mirror ratio

LNA Low-noise amplifier

LO Local oscillator

$M_{1}$  *n* MOS transistor number

MASH Multi-stage noise shaping

MOS Metal oxide semiconductor

MOSFET Metal oxide semiconductor field effect transistor

MOSFET-C Filter technique that uses MOSFETs, capacitors, and op-

erational amplifiers

NMOS N-channel metal oxide semiconductor

OTA Operational transconductance amplifier

PDA Personal digital assistant

PMOS P-channel metal oxide semiconductor

R Resistor

R<sub>ON</sub> MOS switch transistor on-resistance

R<sub>S</sub> Receiver input impedance

RF Radio frequency

RFID Radio frequency identification

rms Root-mean-square

RSD Redundant sign digit

RSSI Received signal strength indicator

RX Receiver

S<sup>2</sup>I Current-mode double-sampling

$S_{1...n}$  Switch number

S/H Sample-and-hold

SC Switched-capacitor

SI Switched-current

SO Switched-opamp

SoC System on chip

UWB Ultra wideband

WCDMA Wideband code division multiple access

WLAN Wireless local area network

## **Chapter 1**

## Introduction

#### 1.1 Motivation for the Thesis

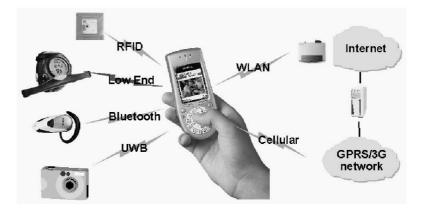

Wireless sensors are small devices, intended to operate for several years without a battery change. Since they are wireless, they are optimal for monitoring hte environment and weather. Devices present in everyday life, such as a mobile phone or personal digital assistant (PDA) could act as a terminal and a gateway to internet and mobile networks for different sensors and short-range applications, as shown in Figure 1.1.

Extremely low power dissipation and material costs are the key requirements for battery-powered sensor modules. With modern deep sub-micron complementary metal oxide semiconductor (CMOS) processes, the cost-effective integration of a whole system on chip (SoC) is possible. Hence, for long stand-alone operation and cost-effective realization, minimizing power dissipation and silicon area are the main design targets.

**Figure 1.1** Mobile phone as a gateway to internet and mobile networks.

2 Introduction

From the sensor radio receiver point of view, a high integration level can be achieved by using, for example, the direct conversion receiver architecture. The demand for low costs requires the use of CMOS technology without additional process options, such as high-quality resistors or capacitors. However, what makes the realization challenging is the fact that in deep sub-micron processes the available gain from a single transistor is only moderate. In addition, in a CMOS direct conversion receiver, the flicker noise increases the noise figure (NF) significantly. These two facts reduce the available operating range. However, since sensors are typically short-range devices, the reduction in operating range can be tolerated [4].

There are different solutions for wireless sensor networks on the market. However, the large number of radios required by various wireless standards makes the mobile phone design challenging. In addition, most of the solutions consume too much power for applications, such as wristtop computers. Hence, to fulfill the requirements for low power dissipation and to be able to utilize existing short-range radios in mobile phones, new low-power solutions based on existing short-range radios are required.

A mobile terminal used as a terminal should be capable of operating in the widely used global system for mobile communications (GSM) networks, as well as in third-generation wideband code division multiple access (WCDMA) networks, while having very low power dissipation in order to extend the life-time of the battery.

For sensor interfaces designed to read actual sensors, for example accelerometers, the design targets are rather similar. In every sensor interface, to be able to use digital signal processing, the measured analog data have to be converted into digital form. Hence, an A/D converter is required that is capable of meeting stringent requirements for both power dissipation and silicon area. In addition, flexibility in the A/D converter topology is preferred, since it enables the same circuit block to be used for tasks with different requirements for speed and accuracy.

## 1.2 Analog Circuit Design in Deep Sub-Micron CMOS

When deep sub-micron processes are used for analog design, most of the technology changes make the analog design even more challenging. With deep sub-micron processes, the available power supply is 1.2 V or less, and therefore the signal headroom required in analog designs is relatively small. The signal range in most of the analog blocks is reduced and cascode structures cannot be used, forcing the circuit solutions toward folded and cascade structures. Furthermore, as the supply voltage is reduced, the achievable linear range is narrowed, thus reducing the linear operation range. This makes the operation of metal oxide semiconductor (MOS) switches and MOS-resistances critical. With very short channel lengths, the source/drain contacts are reduced to only one, which can lead to increased resistance which is not desirable

especially in fast-operating switches. Furthermore, the matching of very short-channel transistors is poor, and in pure analog design, transistors with a minimum channel length are seldom, if ever, utilized.

One of the benefits of technology scaling in analog design is the increased bandwidth, which makes possible better RF and high frequency operation. On the other hand, the achievable speed can also be traded for reduced power dissipation. Even though amplifiers, for example, can be designed for higher bandwidth, the increase is only proportional to the scaling of the channel length. As a drawback, in deep submicron processes, the gain from a single transistor is moderate, making the design of applications requiring a high gain hard. Fortunately, some of the processes have options for high-voltage transistors, which can operate with higher supply voltages. With these transistors, analog applications requiring a large headroom can be implemented, while digital blocks can benefit from the technology scaling.

In this thesis, several solutions from different design aspects are presented to overcome the design challenges in deep sub-micron design. Some solutions are based on new circuit structures that are capable of operating with very low supply voltages [P1, P2, 1]. Some solutions utilize existing circuit structures whose operation is optimized for low-voltage operation, and take advantage of increased speed in deep sub-micron CMOS [P3]. Finally, some solutions utilize high-voltage transistors to implement analog circuits requiring supply voltages over 1.2V, while having very low power dissipation [P4, P6, P5, 2, 3].

## 1.3 Research Contribution

The research described in this thesis focuses on low-power sensor applications.

The author has designed and implemented baseband circuitry for direct conversion receivers for ubiquitous communications. The first prototype was published in [P1,1]. The whole system was implemented in [P2]; however, only the receiver part implemented by the authors was reported. The other team members were Mr. J. Kaukovuori, D.Sc J. Jussila, and Prof. J. Ryynänen. Mr. J. Kaukovuori and Prof. J. Ryynänen were responsible for the RF front-end design. The author was responsible for the analog baseband circuitry, together with D.Sc J. Jussila. The project demonstrated that in ubiquitous communications, the power dissipation can be reduced significantly from that found in the solutions presently on the market.

The design possibilities with deep sub-micron CMOS processes were studied in a project in which a low-pass  $\Delta\Sigma$  modulator was designed and implemented for a direct conversion receiver [P3]. The main objective was to find out, what the design challenges are and what kind of performance can be achieved. The other team members were Mr. J. Kaukovuori and Prof. J. Ryynänen, who were responsible for the

4 Introduction

RF front-end. The author was responsible for the  $\Delta\Sigma$  modulator design. The project demonstrated, that with deep sub-micron CMOS processes, high-performance designs can be achieved using robust circuit structures with careful design.

Sensor applications were again studied in a project in which the author designed and implemented algorithmic A/D converters for a capacitive sensor interface. Various innovative A/D converter topologies were developed by the author in order to minimize the power dissipation and silicon area of the A/D converter [P4, P6, 3]. The whole system was published in [P5, 2]. The other team members were Lic.Sc M. Paavola, Lic.Sc M. Kämäräinen, Mr. M. Saukoski, and D.Sc M. Laiho.

## 1.4 Organization of the Thesis

This thesis is divided into two parts. In the first part, the issues related to direct conversion receiver design are covered. The existing solutions for ubiquitous communications are briefly covered and the proposed system is described. The main focus is on the baseband circuit design.

The second part considers low-power A/D converter design. The emphasis is on the design and implementation of A/D converter topologies suitable for sensor applications and mobile terminals.

## **Chapter 2**

# **Baseband Circuits for Wireless Sensors**

#### 2.1 General

In recent years, wireless sensor networks that do not require high speed or accuracy have been gaining more attention in the field of wireless data transmission and networking [5–18]. Sensor networks can be made up of hundreds of nodes, and therefore each sensing node needs to be inexpensive and compact, while still providing reliable and accurate sensing and data transmission. Sensors are typically short-range devices [4] and data are transmitted in a peer-to-peer fashion over short distances ( $\sim$ 10 m) at relatively low data rates (<500 kbps). Typically, the main design target for these systems is a very low power dissipation. Since sensors are typically battery-powered devices, to achieve stand-alone operation for over one year, extremely small active and stand-by currents are required. Furthermore, the requirement to implement an inexpensive and compact system leads to a small device with a minimum number of external components. A high integration level can be achieved by using, for example, a direct-conversion receiver.

Sensors can be utilized in different places such as office buildings, homes, and schools. Wireless sensors are convenient for monitoring the environment and weather. Sensors can monitor, for example, temperature, wind, pressure, direction, and acceleration. The actual sensing element can be integrated into the sensor itself, or the sensor can be used to transfer the data from an external measurement instrument to a user interface. In addition to different measurement applications, other small devices would also benefit from the short range, low data rate, and wireless connectivity. A mobile terminal is a suitable user interface for the sensors, since most people carry

one with them all the time. Standard Bluetooth radio [19] is implemented in most modern mobile terminals. However, the standard Bluetooth radio's power dissipation and capability of handling a large number of sensor nodes power efficiently are not suitable for low-power wireless sensor systems. Hence, to fulfill requirements for low power dissipation and to be able to utilize existing Bluetooth radios in mobile phones, a low power version of Bluetooth radio with slight changes in the radio parameters was introduced [20].

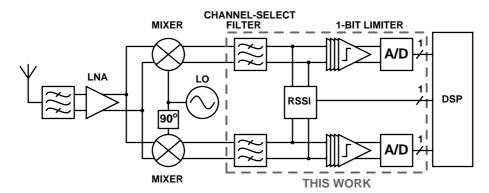

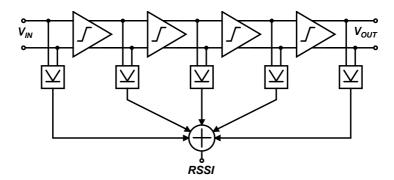

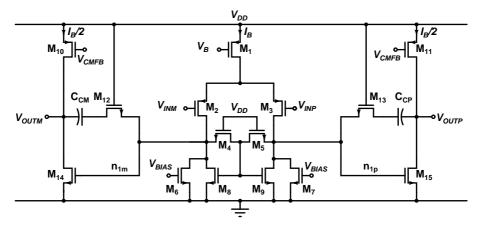

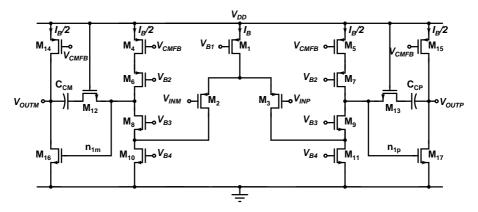

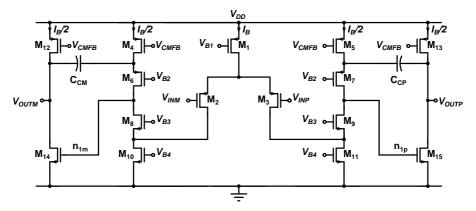

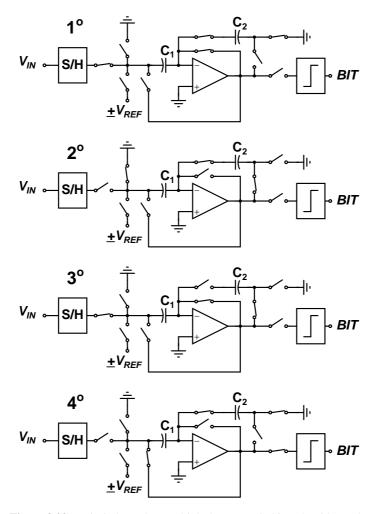

The architecture of the implemented wireless direct-conversion sensor receiver is shown in Figure 2.1. The total system architecture and system specifications are presented in [20], and the receiver design is presented in [P1,P2]. The implemented baseband circuits in this thesis include a mixer-baseband interface, channel-select filter, 1-bit limiters for the A/D conversion, and a one-level received signal strength indicator (RSSI) for signal level detection. The 1-bit resolution, together with the large modulation index, makes the receiver insensitive to strong reception signals [20]. In the following sections, specifications and an overview of the implemented building blocks are given.

Figure 2.1 Direct-conversion wireless sensor receiver.

## 2.2 Specifications for Sensor Baseband Circuits

In this section, important specifications used to measure radio receivers are reviewed. The emphasis is on specifications that are important for baseband building blocks. Some measures that enable different filter and limiter realizations to be compared are also given.

#### 2.2.1 Noise Figure and Baseband Noise

In low-power direct-conversion wireless receivers implemented using deep sub-micron CMOS processes, the *NF* of the receiver is typically dominated by the flicker noise in direct-conversion mixers. However, in order not to further degrade the *NF* of the whole receiver, the noise contribution of the baseband circuits should be minimized. The output noise of the baseband (BB) referred to receiver (RX) input can be calculated using (2.1) [21]

$$v_{n,out,BB} = A_{V,RX} \sqrt{\left(10^{(NF_{RX}/10)} - 10^{(NF_{RF}/10)}\right) kT 2f_{bb}R_S},$$

(2.1)

where  $NF_{RX}$  is the receiver NF,  $NF_{RF}$  is the front-end NF, k is the Boltzmann constant, T is the absolute temperature,  $f_{bb}$  is the baseband bandwidth, and  $R_S$  is the receiver input impedance.

### 2.2.2 Linearity

The output signal of a memoryless nonlinear system can be expressed using a Taylor series expansion

$$V_{OUT} = k_0 + k_1 V_{IN} + k_2 V_{IN}^2 + k_3 V_{IN}^3 + \dots + k_n V_{IN}^n,$$

(2.2)

where  $V_{IN}$  is the input signal voltage, the coefficient  $k_0$  is a DC offset,  $k_1$  is the linear gain of the system, and the coefficients  $k_2, k_3, \ldots, k_n$  represent the system nonlinearity.

Typically, a two-tone test is used to measure the linearity of a radio receiver. In the two-tone test, two sinusoidal test signals with equal amplitude V and some frequency offset are fed into a nonlinear system described by (2.2). The resulting input signal with input signal frequencies  $\omega_1$  and  $\omega_2$  is

$$V_{IN}(t) = V\left(\cos(\omega_1 t) + \cos(\omega_2 t)\right) \tag{2.3}$$

At the output, only second- and third-order distortion components are taken into account. The resulting low-frequency second-order *intermodulation distortion (IMD)* that falls into the baseband filter passband is

$$V_{IMD2}(t) = k_2 V^2 \cos((\omega_1 - \omega_2)t). \tag{2.4}$$

The frequencies are chosen to be such that  $\omega_1 - \omega_2 < \omega_{bb}$ , where  $\omega_{bb}$  is the baseband passband edge corner frequency. The resulting low-frequency third-order *IMD* that

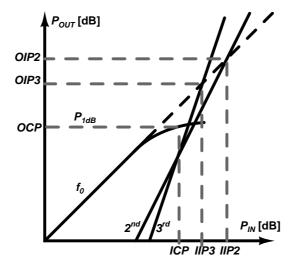

Figure 2.2 The definition of the intercept points and the 1-dB compression point.

falls into the baseband filter passband is

$$V_{IMD3}(t) = \frac{3}{4}k_3V^3\cos((2\omega_1 - \omega_2)t)$$

(2.5)

Here the frequencies are chosen to be such that  $\omega_1 < \omega_2$ , and  $2\omega_1 - \omega_2 < \omega_{bb}$ .

The definitions of the intercept points and the 1-dB compression point at the input and the output are shown in Figure 2.2. The second- and third-order intercept points are defined as the input powers, where the extrapolated output signal crosses the second-or third-order *IMD* lines.

The second-order input intercept point (IIP2) is given by

$$IIP2 = 2P_{IN} - P_{IMD2.IN} = OIP2 - G,$$

(2.6)

where  $P_{IN}$  is the input power of each two-tone test signal,  $P_{IMD2,IN}$  is the second-order IMD component at the input, G is the passband gain, and OIP2 is the second-order output intercept point.

The third-order input intercept point (IIP3) is given by

$$IIP3 = \frac{3P_{IN} - P_{IMD3,IN}}{2} = OIP3 - G,$$

(2.7)

where  $P_{IMD3,IN}$  is the third-order IMD component at the input, and OIP3 is the third-order output intercept point.

When a single-tone signal with an amplitude V and a frequency of  $\omega_1$  is fed into a

nonlinear system described by (2.2), the resulting fundamental output signal at  $\omega_1$  is

$$V_{OUT} = \left(k_1 V + \frac{3k_3 V^3}{4}\right) \cos(\omega_1 t). \tag{2.8}$$

If the coefficients  $k_1$  and  $k_3$  have opposite signs, the output starts to compress at some input signal level. The input signal power at which the gain is reduced by 1 dB compared to the linear gain is called the *input compression point (ICP)*. The *OCP* is the output compression point.

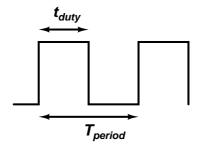

#### 2.2.3 Duty Cycle

A duty cycle is an important parameter in limiting amplifiers, since deviation from 50% in the duty cycle degrades the achievable signal-to-noise ratio [22]. In limiter design, the duty cycle is measured to define how much the limited output differs from the ideal with a sine wave input signal. The duty cycle shown in Figure 2.3 is defined as

$$D = \frac{t_{duty}}{T_{period}} \cdot 100\% \tag{2.9}$$

where  $t_{duty}$  is the duration that the output signal is non-zero, and  $T_{period}$  is the signal period. For a pure sine wave input signal with a zero offset, the limited output duty cycle is ideally 50%. In reality, some offset voltage exists at the limiter input and degrades the duty cycle, as shown in (2.10).

$$D = \frac{t_{duty}}{T_{period}} \cdot = \frac{1}{2} \left( 1 + \frac{V_{OFF}}{V_{SIG}} \right) \cdot 100\%, \tag{2.10}$$

where  $V_{OFF}$  is the offset voltage and  $V_{SIG}$  is the amplitude of the signal. For a limited signal, the signal amplitude is half of the signal range.

Figure 2.3 Duty cycle.

# 2.2.4 Group Delay and AM-to-PM conversion

The group delay is defined as a signal propagation delay variation through the system with different input signal levels, causing phase shift. However, for limiting amplifiers, the propagation delay depends on the signal level, whereas the group delay variation as a function of input signal frequency is negligible. Hence, limiting amplifiers convert amplitude variation into phase fluctuations, phenomena also called amplitude variation to phase deviation (AM-to-PM) [22, 23]. Amplitude variation can result from the user abruptly moving the receiver terminal nearer to or away from the sensor. This can potentially degrade the signal-to-noise ratio in a phase-sensitive FSK detector [22]. In this work, group delays measured in [P1,P2] are considered as a AM-to-PM conversion and measured as a variation in the propagation delay at a single input signal frequency with different input signal levels, as was also done in [22].

# 2.2.5 Start-up Time

In sensor systems, the receiver can be idle for long periods of time and will wake up only when something has to be received. Hence the stand-by time of the system can be significantly improved if the power dissipation in the idle mode can be designed to be negligible. However, if the system often alternates between active and idle modes, the system start-up time must be kept short in order to minimize power dissipation [P1]. The start-up time is defined as the time from the wake-up signal until the system has started. In this work, the start-up time was measured in [P1] from the baseband filter output, which excludes the start-up delay caused by the limiter. In [P2], the start-up time was measured from the limiter output, which gives the real start-up time of the whole system.

# 2.2.6 Filter Performance Comparison

To be able to compare different filter realizations for short-range communications, a figure of merit that gives the filter power dissipation per pole is given by

$$FOM_F = \frac{P_D}{Order \cdot f_{bb}},\tag{2.11}$$

where  $P_D$  is the filter power dissipation, *Order* is the filter order, and  $f_{bb}$  is the baseband bandwidth.

# 2.3 Sensor Baseband Circuits

In a wireless direct-conversion sensor receiver, the baseband typically includes channel-select filters, some sort of A/D conversion, and input signal level detection. In sensor receivers, the A/D conversion can be implemented using a limiter, giving a 1-bit A/D conversion. The benefit of 1-bit A/D conversion is insensitivity to strong reception signals, since the input signal is always limited. Hence the A/D converter, namely the limiter, is never overloaded. Input signal level detection is used to control the received and transmitted power levels. In this section, an introduction to the channel-select filters, limiters, and input signal level detection circuits for wireless sensor receivers is given. The sensor baseband circuits designed in this thesis are published in papers [P1, P2, 1].

# 2.3.1 Mixer-Baseband Interface

The mixer predominantly used in direct-conversion receivers is a Gilbert-cell mixer. The output of a Gilbert-cell mixer is current. Hence, the mixer-baseband interface can be a current- or voltage-mode interface. In a voltage-mode interface the signal current is driven to a high-impedance node, resulting in a voltage swing at the mixer output. The front-end voltage gain is now determined from the low-noise amplifier (LNA) input to the mixer output. In a current-mode interface the signal current is driven to a low-impedance node. Hence there is no voltage swing at the mixer output, and the signal current is converted to a voltage at the output of the first baseband stage. Therefore, the front-end voltage gain will be merged with the gain of the first baseband stage, and is now determined from the LNA input to the output of the first baseband stage. Next, some voltage- and current-mode interface topologies are discussed.

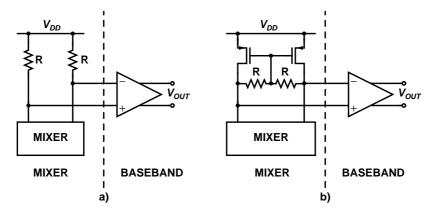

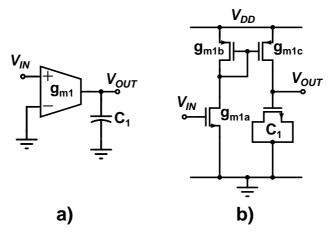

Two voltage-mode mixer-baseband interfaces are shown in Figure 2.4. The high-impedance interface required for the voltage-mode operation can be implemented using an operational amplifier [7, 16] or just a MOS transistor [8]. The voltage-mode mixer-baseband interface with load resistors in Figure 2.4 a) is implemented in [7, 8, 16]. In this solution, the resistance values determine the voltage gain from the LNA input to the mixer output. However, the mixer bias current and supply voltage limit the feasible resistance values. Adding current sources in parallel with the resistances would reduce the bias current flowing through the resistors, allowing higher resistance values, and would result in an increased impedance level and voltage gain. However, additional current sources will add another noise source to the interface. The voltage-mode mixer-baseband interface with floating load resistors and current sources in Figure 2.4 b) is implemented in [11, 22]. Now the whole current drawn by the mixer flows through current source transistors, resulting in increased noise. However, the resistance values can be increased for larger voltage gain. Resistances also take care of the common-

Figure 2.4 Different voltage-mode mixer-baseband interfaces.

Figure 2.5 Different current-mode mixer-baseband interfaces.

mode feedback circuit (CMFB). For all-MOS realization, the resistances would have to be removed and the transistors would have to have separate diode-connections, making the mixer load impedance  $\sim 1/g_m$ , where  $g_m$  is the transistor transconductance. In many cases, the impedance level is insufficient, resulting in poor voltage gain and increased NF in the receiver. The impedance level could again be increased by adding current sources in parallel, again adding another noise source to the interface.

Two different current-mode mixer-baseband interfaces are shown in Figure 2.5. The low-impedance node required for the current-mode operation can be, for example, a transimpedance amplifier input or a cascode transistor source. Furthermore the mixer bias current can be optimized, since the biasing is based purely on current sources [P1]. The current mode mixer-baseband interface can be implemented using current source

loads, as shown in Figure 2.5 a) [24]. In this realization, the low-impedance node is implemented using a transimpedance amplifier. This transimpedance amplifier can be used as the first stage of a lossy active-RC integrator [24], in which integrating capacitors are added in parallel with the feedback resistor. If a lossless active-RC integrator is used, an additional DC feedback loop has to be implemented to provide appropriate biasing.

The current mode mixer-baseband interface can also be implemented using cascode transistors, as shown in Figure 2.5 b) [P1,P2]. N-channel MOS (NMOS) cascode transistors can be removed for operation with a very low power supply. If required, the impedance level at the P-channel MOS (PMOS) cascode transistor sources can be lowered using regulated PMOS cascode transistors, in which a feedback amplifier is used to keep the cascode transistor drain-source voltage as stable as possible [25,26]. Compared to the topology in Figure 2.5 a), the current through the PMOS current sources is larger, resulting in increased noise. However, neither operational amplifiers nor resistors are required, making the topology suitable for all-MOS realizations. Furthermore, the topology is well suited to operation with a very low supply voltage.

It can be concluded, that for low-voltage applications, a current-mode interface is more suitable, since there is no voltage signal at the mixer output. Hence the mixer does not require additional headroom for voltage swing. The noise contribution of the current-mode interface is equal to or larger than that in the voltage-mode interface [21]. However, in sensor applications, some operating range can be traded for noise. Finally, the current-mode interface topology shown in Figure 2.5 b) is well suited for all-MOS realizations.

## 2.3.2 Continuous-Time Active Filters

The most popular baseband filter architectures for sensor receivers are active-RC [7, 11, 14, 27] and  $g_m$ -C [8, 12, 28, 29]. Next, the two filter topologies are introduced.

# 2.3.2.1 Active-RC

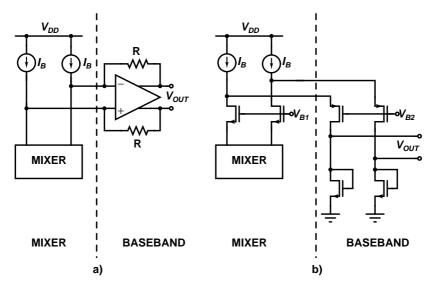

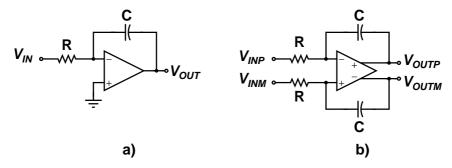

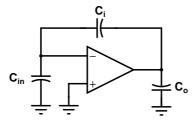

A very popular continuous-time filter topology is based on an inverting active-RC integrator shown in Figure 2.6. In practice, the fully differential structure shown in Figure 2.6 b) is used, since it is less sensitive to power supply noise and even-order harmonic distortion. However, the required silicon area is approximately doubled. The active-RC integrator requires a resistor, an operational amplifier, and a capacitor in a negative feedback loop. As a result of the negative feedback loop, there is a virtual ground at the operational amplifier inputs. When the input signal voltage is applied, the input resistor R transforms the input voltage into a current, which is integrated by the feedback capacitor C. The resulting transfer function for the active-RC integrator

Figure 2.6 a) A single-ended active-RC integrator. b) A fully differential active-RC integrator.

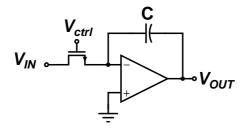

Figure 2.7 a) A single-ended MOSFET-C integrator.

in the s-domain is

$$V_{OUT}(s) = -\frac{1}{sRC}V_{IN}.$$

(2.12)

The benefits of the active-RC integrator are that as a result of the virtual ground, different input signals can be summed at the operational amplifier input without any additional active components by adding an another input resistor. In addition, lossy integrators can be implemented, without any additional current, by adding a resistor in parallel with the integrating capacitor. Additionally, the active-RC integrator is insensitive to parasitic capacitances, since the input and the output of the operational amplifier have well-controlled voltages. The drawback of active-RC integrators is that the filter time constant varies considerably as a result of variations in temperature and process, since the variations in the resistors and capacitors do not correlate. Hence, in practice, the time constants are tuned using parallel integrating capacitors, resulting in increased silicon area. The silicon area can be reduced using MOSFET-C integrators, in which the resistor is replaced with a MOS-transistor operating in a triode-region, as shown in Figure 2.7. The area required by the transistors is much less than that required by the resistors. In addition, the filter time constants can be tuned by changing the control voltage  $V_{ctrl}$  at the MOS-transistor gate. The drawback of the solution is a reduced linear signal range.

**Figure 2.8** The single-ended  $g_m$ -C integrator.

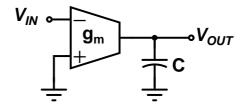

#### 2.3.2.2 $g_m$ -C

Another widely used continuous-time integrated filter technique is a  $g_m$ -C filter. A single-ended inverting  $g_m$ -C integrator used in  $g_m$ -C filters is shown in Figure 2.8. The input voltage at the input of a voltage-to-current converter or transconductor [30] with a transconductance  $g_m$  is converted to a current at the transconductor output, where it is integrated by the capacitor C. The resulting transfer function for the  $g_m$ -C integrator in the s-domain is

$$V_{OUT}(s) = -\frac{g_m}{sC}V_{IN}. (2.13)$$

Typically, for linear transconductors, a combination of several transistors is used, each contributing noise. Hence, compared to the RC integrator, the noise of the  $g_m$ -C integrator is significantly higher, with values of 2 to 3 being common [31]. While the active-RC integrator does not require additional active components for input signal summing and for lossy integrators, the  $g_m$ -C integrator requires additional parallel transconductors for summing different input signals and for realizing the lossy integrator shown in Figure 2.13.

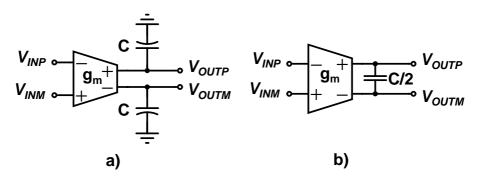

Because of their better immunity to power supply noise and even-order harmonic distortion,  $g_m$ -C filters are also implemented using a fully differential  $g_m$ -C integrator as shown in Figure 2.9 a). The fully differential structure doubles the total capacitance, as is the case for active-RC realizations (Figure 2.6), where the resistance is also doubled. Fortunately, a fully differential  $g_m$ -C integrator with a floating capacitor, as shown in Figure 2.9 b), can be used to reduce the total capacitance to one quarter of the original capacitance. In applications, where the silicon area should be minimized, this gives a great advantage over active-RC realizations.

The  $g_m$ -C filter time constant also varies as a result of temperature and process variations. However, tuning the  $g_m$ -C filters time-constants is possible by using capacitor arrays, as in active-RC filters, or tuning the bias currents, in which case continuous tuning becomes possible. Invariably, the use of continuous tuning brings some loss of maximum signal handling capability [31,32]. However, the savings in silicon area and the much better tuning accuracy act in favor of bias current tuning.

$g_m$ -C integrators are sensitive to parasitic capacitances at the output of a transcon-

**Figure 2.9** a) A fully differential  $g_m$ -C integrator. b) A fully differential  $g_m$ -C integrator with a floating capacitor.

**Figure 2.10** A single-ended  $g_m$ -C-OTA integrator.

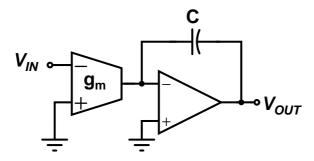

ductor. The effect of the parasitic capacitances can be greatly reduced by using an operational transconductance amplifier (OTA), discussed later in Section 3.3.1, in the  $g_m$ -C-OTA integrator shown in Figure 2.10 [33].

For modest linearity applications, such as sensor receivers, MOS transistors may replace the capacitors, thus allowing a high capacitance per unit area and implementation in fabrication processes intended for purely digital very large-scale integration [34]. However, floating capacitors are hard to implement using only MOS transistors. Hence, in all-MOS realizations, structures with grounded capacitors are preferred, eliminating structures with floating capacitors, such as the fully differential  $g_m$ -C integrator with a floating capacitor in Figure 2.9 b) and in the  $g_m$ -C-OTA integrator. However, the  $g_m$ -C-OTA integrator can be implemented using PMOS transistors operating in the triode region, since the common-mode levels at the input and output of the OTA can be different, making possible the appropriate voltage over the PMOS transistors [35].

## 2.3.2.3 All-MOS $g_m$ -C Filter

For sensor receivers operating on a single button cell battery, the key requirements are extremely low power dissipation and material costs. In addition, the receiver has to

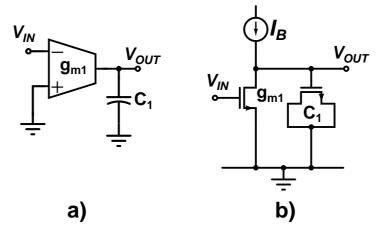

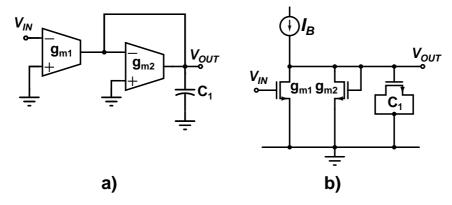

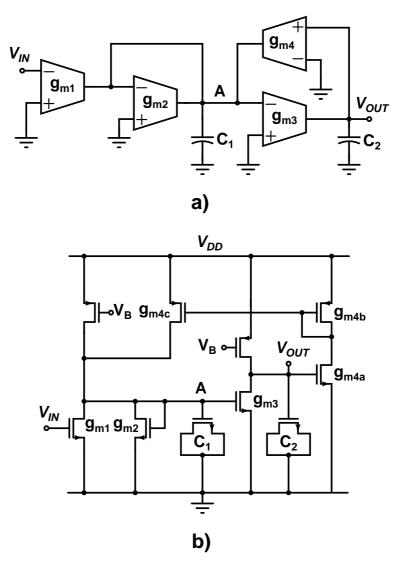

**Figure 2.11** a) The single-ended lossless inverting  $g_m$ -C integrator. b) Equivalent all-MOS transistor implementation.

be able to operate with a supply voltage limited to 1.0-1.5 V. Taking these specifications into account, a suitable filter architecture for sensor receivers is the  $g_m$ -C filter. Furthermore, a simple realization using only MOS transistors results in a small area and compatibility with processes optimized for digital signal processing. Even though the fully differential structures are less sensitive to noise and distortion, the use of two single-ended circuits without intermediate cross-connections, a so-called pseudo-differential structure [28], is a good alternative. This structure does not need a CMFB circuit, which helps the design when using low supply voltages. However, the structure offers no common-mode rejection. Hence, mismatches in the pseudo-differential signal chains convert some of the common-mode signal to differential. Next, basic single-ended building blocks for all-MOS  $g_m$ -C filters are discussed.

A single-ended lossless inverting  $g_m$ -C integrator and its equivalent all-MOS transistor implementation are shown in Figure 2.11. A non-inverting counterpart is shown in Figure 2.12. The MOS capacitor is implemented using a NMOS transistor in inversion. An accumulation region PMOS transistor would be more linear [34], but implementing both the transconductor and MOS capacitor with the same type of transistor results in better matching in process variations. To make it possible to implement a lossy  $g_m$ -C integrator, an additional transconductor is required, as shown in Figure 2.13.

Using the building blocks described above, the single-ended all-MOS  $g_m$ -C biquad shown in Figure 2.14 can be implemented [P1]. A biquad using similar building blocks to those described above is presented in [36]. However, this biquad structure requires floating capacitors, making an all-MOS implementation difficult.

Higher even-order filters can be implemented by cascading the biquad stages. For

**Figure 2.12** a) The single-ended lossless non-inverting  $g_m$ -C integrator. b) Equivalent all-MOS transistor implementation.

**Figure 2.13** a) The single-ended lossy inverting  $g_m$ -C integrator. b) Equivalent all-MOS transistor implementation.

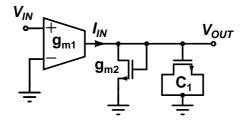

the odd-order filters, one of the poles lies on the real axis of the s-plane. Thus the pole can be realized by using passive components available in an analog process [37, 38]. In an all-MOS realization, the pole can be implemented for a current-mode input signal  $I_{IN}$  with a diode-connected MOS transistor and a MOS capacitor, as shown in Figure 2.15. This kind of structure is used in [P1, P2] to implement the real pole in the mixer-baseband interface. In [P2], a second real pole is implemented to provide an additional attenuation of strong out-of-band interfering signals. Using the building blocks described above, higher-order filters can also be implemented with a leapfrog structure, resulting in lower sensitivity to component variations.

**Figure 2.14** a) The single-ended  $g_m$ -C biquad prototype. b) Equivalent all-MOS transistor implementation.

Figure 2.15 An all-MOS real pole with a current-mode input signal.

# 2.3.2.4 Comparison of Active-RC and $g_m$ -C Filters

At low frequencies, where sensor applications are used,  $g_m$ -C filters dissipate less power and have smaller silicon area than active-RC filters, whereas active-RC filters have better dynamic range and noise properties [21,31,32]. As mentioned earlier, extremely low power dissipation and material costs are the key requirements for battery-powered sensor modules. Hence, in sensor receivers, good dynamic range and noise properties can be traded for low power and a reduced silicon area. The continuous-time filters for sensor receivers are compared using (2.11) in Table 2.1. Table 2.1 shows that the top four filters in terms of low energy dissipation per pole ( $FOM_F$ ), are  $g_m$ -C filters. Furthermore, the top five filters in terms of low power dissipation are  $g_m$ -C filters.

| Ref. | Year | Gain [dB]        | $P_D [\mu W]$     | $f_{bb}[kHz]$ | Order | Arch.             | $FOM_F$ [nJ] |

|------|------|------------------|-------------------|---------------|-------|-------------------|--------------|

| [28] | 1999 | 0                | 10.5              | 100           | 5     | g <sub>m</sub> -C | 0.02         |

| [7]  | 2000 | 20               | 210               | 25            | 4     | Active-RC         | 2.10         |

| [8]  | 2001 | 0                | 100               | 100           | 5     | $g_m$ -C          | 0.20         |

| [11] | 2003 | 12.4             | 2520              | 2200          | 5     | Active-RC         | 0.23         |

| [12] | 2003 | 20               | 4000              | 500           | 4     | g <sub>m</sub> -C | 2.00         |

| [29] | 2003 | 0                | 167               | 50            | 3     | $g_m$ -C          | 1.11         |

| [14] | 2004 | 20               | 600               | 120           | 3     | Active-RC         | 1.67         |

| [27] | 2004 | 55               | 4860              | 1000          | 6     | Active-RC         | 0.81         |

| [P1] | 2005 | 9.5 <sup>1</sup> | 78 <sup>2</sup>   | 550           | 3     | $g_m$ -C          | 0.05         |

| [P2] | 2006 | 9.5 <sup>1</sup> | 48 <sup>2,3</sup> | 546           | 4     | $g_m$ -C          | 0.02         |

Table 2.1 Comparison of Continuous-Time Filters

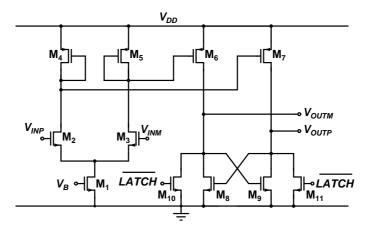

# 2.3.3 Limiter and Received Signal Strength Indicator

In wireless systems, detecting the strength of the incoming signal enables both the receiver gain and the transmitted power to be adjusted in order to optimize the system performance. The gain control can be implemented using either an automatic gain control (AGC) amplifier or a limiter. A limiter or a limiting amplifier is a chain of cascaded gain stages that saturate the input signal to a constant value. For wireless sensor networks, the limiter is preferred to AGC since it can handle a larger dynamic range while consuming less power [39]. In addition, limiters can be used for 1-bit A/D-conversion [P2, 20]. Since the limiter limits the incoming signal, it loses the incoming signal strength information. However, a RSSI can be used together with the limiter to detect the level of the incoming signal. Hence the adjustment of either the gain of the limiter or the transmitted power is possible. Since limiters are typically implemented

<sup>&</sup>lt;sup>1</sup> Gain after the mixer-baseband interface.

<sup>&</sup>lt;sup>2</sup> Includes the mixer-baseband interface current consumption, which is approximately half of the total filter current consumption.

<sup>&</sup>lt;sup>3</sup> Simulated.

Figure 2.16 Limiter with logarithmic RSSI.

together with RSSI circuits, both are next discussed simultaneously.

A successive-detection logarithmic amplifier [40], shown in Fig. 2.16, is typically used in RSSI implementations in wireless receivers. In this kind of structure, the logarithmic response is achieved via piecewise linear approximation. The benefits of the logarithmic amplifier are that it can handle a wide dynamic range, together with accurate signal level detection. If accurate signal level detection is not required, the RSSI can implement only a single detection level [P2].

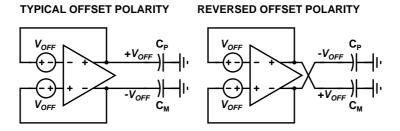

# 2.3.3.1 DC Offset Compensation Techniques for Limiters

Since a limiter is a chain of cascaded gain stages and has a very high gain, even a small offset voltage resulting from mismatches or from preceding stages may saturate the output of the limiter. Hence, DC offset compensation techniques have to be used. Next, some DC offset compensation schemes from the literature are discussed.

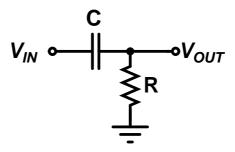

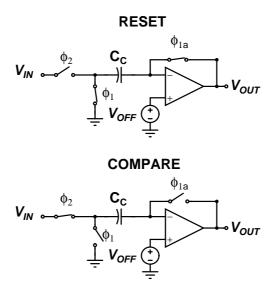

The AC coupling technique removes DC offset from the circuit output [41]. A circuit that performs AC coupling is shown in Figure 2.17. The transfer function of the circuit is

$$H_{AC}(s) = \frac{sRC}{1 + sRC}. (2.14)$$

Figure 2.17 AC coupling.

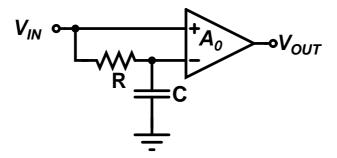

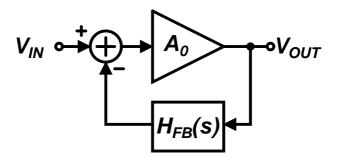

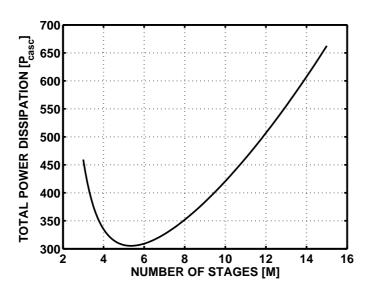

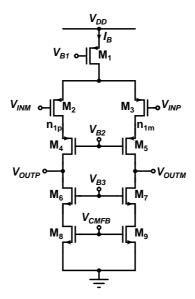

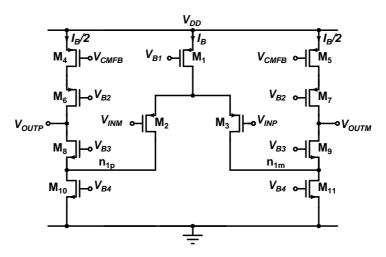

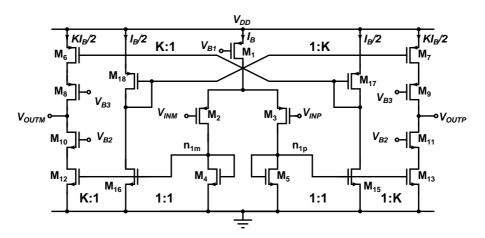

Figure 2.18 The feed-forward offset cancellation technique.